Memory has been in use for over 50 years, and the development and application of semiconductors in the past were not as advanced and diverse as they are today. From earlier PC and laptop products to the applications in mobile phones and mining machines, and now to the trending electric vehicles and AI in 2024, these advancements are driving semiconductors toward new applications.

AI applications require powerful computational capabilities, significantly increasing the proportion of memory within System on Chips (SoC). Traditional March C algorithms can no longer meet the yield requirements of various wafer manufacturers. If algorithms cannot effectively identify memory defects, it will be impossible to repair the chips to a usable state. To fulfill customers’ needs for rigorous and flexible memory testing, and effectively control DPPM (Defective Parts Per Million), iSTARTTEK has developed UDA (User-Defined Algorithm) and EZ-TEC IP to offer customers the optimal testing solutions.

UDA (User-Defined Algorithm)

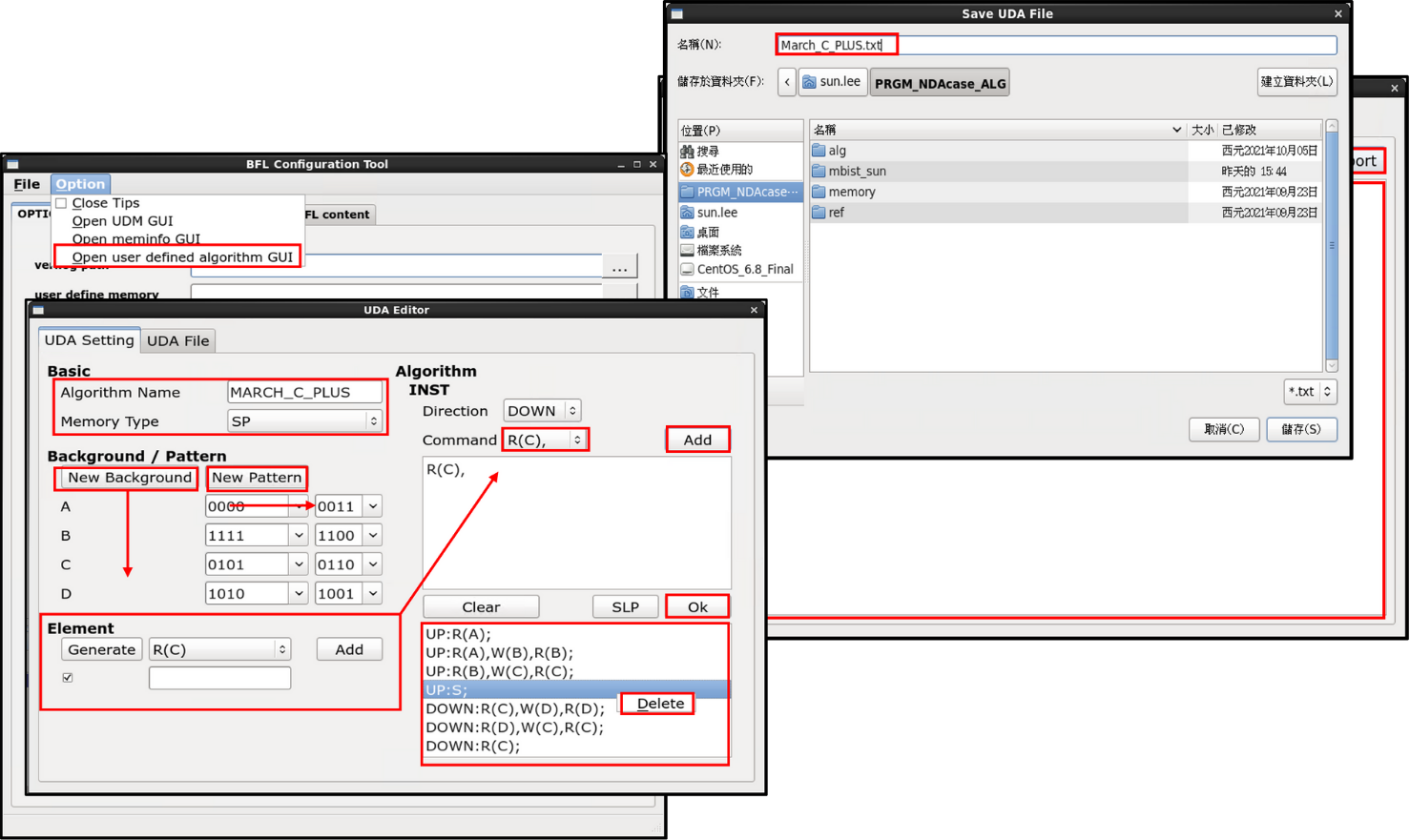

UDA can meet customers’ demands for flexible and user-defined testing algorithms. Design engineers can use GUI (Graphical User Interface) to quickly generate memory testing algorithms. CIM (Computing in Memory) needs to compute directly in memory instead of through the CPU (Central Processing Unit).

In existing testing algorithms, the input and output patterns are identical, meaning that the written data and read data are the same. This allows for comparison of memory data to ensure correctness. Thus, for CIM memory, it is necessary to generate and compare input and output data with different patterns to verify if the CIM memory is functioning correctly.

Easy to Choose Algorithms in GUI of UDA

Easy to Choose Algorithms in GUI of UDA

EZ-TEC SRAM BIST IP

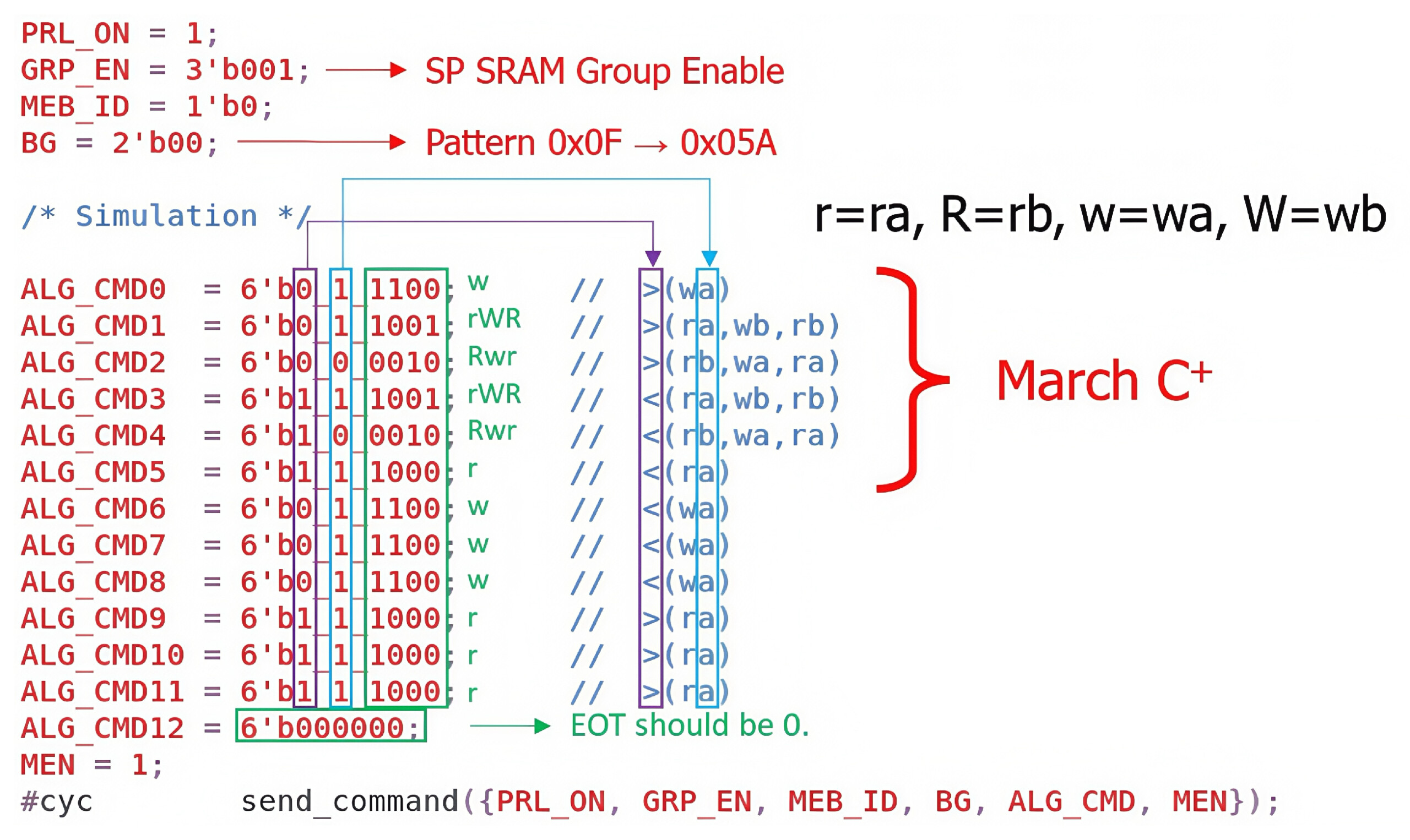

EZ-TEC IP is a modularized architecture SRAM IP developed based on iSTART-TEK’s patent, “METHOD FOR GENERATING A MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT”. Currently, common memory testing algorithms in the market often involve redundant testing, leading to increased testing time and costs. Moreover, as advanced processes continue to progress, existing testing algorithms may fail to detect memory defects in these advanced processes and cannot meet the

evolving demands.

EZ-TEC IP is an advanced technology that effectively addresses this issue by providing test engineers with flexible reconfiguration of testing algorithms. In existing testing algorithms, the execution sequence is fixed once the chip design is completed, making dynamic adjustments impossible during the mass production testing phase. However, EZ-TEC IP allows test engineers to adjust the sequence of test elements, such as W, rWR, and Rwr, during the mass production testing phase according to their needs. Additionally, it is possible to increase or decrease the number of times elements are executed, thereby enhancing the intensity of memory testing. This products and prevents substandard wafers from reaching customers.

Arrangements of Elements

Arrangements of Elements

The UDA combined with EZ-TEC IP can be integrated into a standalone IP, which does not interfere with the customer’s existing DFT solutions. Additionally, it incorporates iSTART-TEK’s solutions, resulting in only a slight increase in the customer’s cost while significantly enhancing chip testing quality.

When incorporating iSTART-TEK’s repair technology, it can further improve the overall chip yield and more effectively reduce DPPM, ensuring the highest quality for the customers’ chips.