The behavior of traditional algorithms cannot be modified if issues occur during Chip Probe (CP) and Final Test (FT) after chip tape-out. iSTART-TEK’s Test Element Change (TEC) function, featuring a Graphical User Interface (GUI), modularizes algorithm behaviors, enabling easy rearrangement and the creation of new test algorithms. This enables dynamic adjustment and element rearrangement during CP and FT testing. Even if customers do not adopt iSTART-TEK’s MBIST circuits, they can retain their original BIST architecture and insert the IP form into the original circuit, providing significant convenience and flexibility in application.

EZ-TEC Architecture

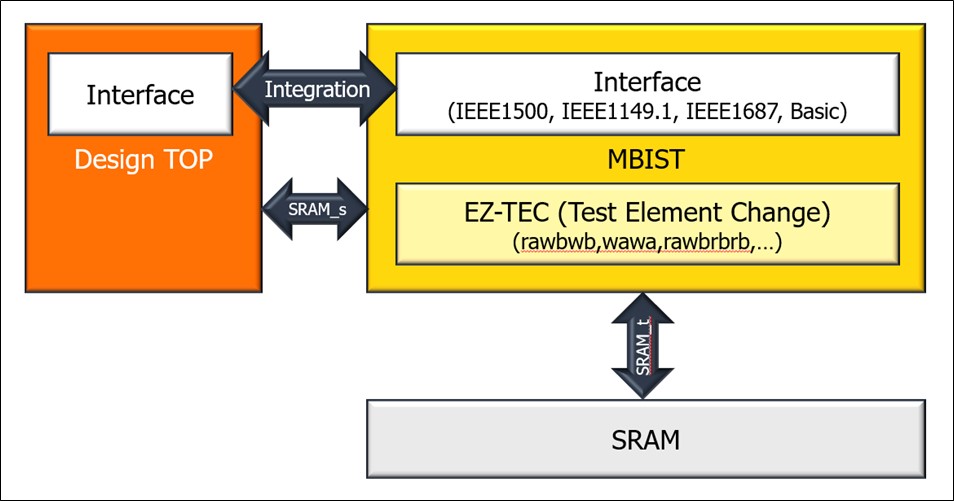

EZ-TEC can be independent with any MBIST EDA tools. Its modularized architecture facilitates the creation of highly cost-effective circuits, and can coexist with the existing memory testing circuits by being inserted beside the critical memory that is to be tested.

EZ-TEC can operate independently from any specific MBIST EDA tools. Its modularized architecture supports the construction of highly cost-effective circuits and can coexist with existing MBIST circuits by being inserted alongside critical memory that requires power-on testing. Here, SRAM_s indicates the original SRAM interface, while SRAM_t represents the SRAM interface processed by the MBIST. By multiplexing the control signals of SRAM, the original architecture is retained, and the new circuit is added in IP form, creating the SRAM_t interface. Finally, it connects to the top level through IEEE1500 or IEEE1149.1 interfaces. Circuit insertion must adhere to each respective clock domain, and once the clock domain is configured with EZ-TEC, the test elements can then connect to the designated SRAM.

Quickly Generate March C+ Algorithms with Elements

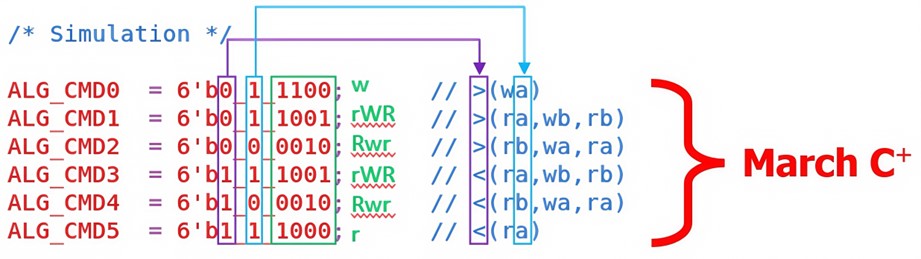

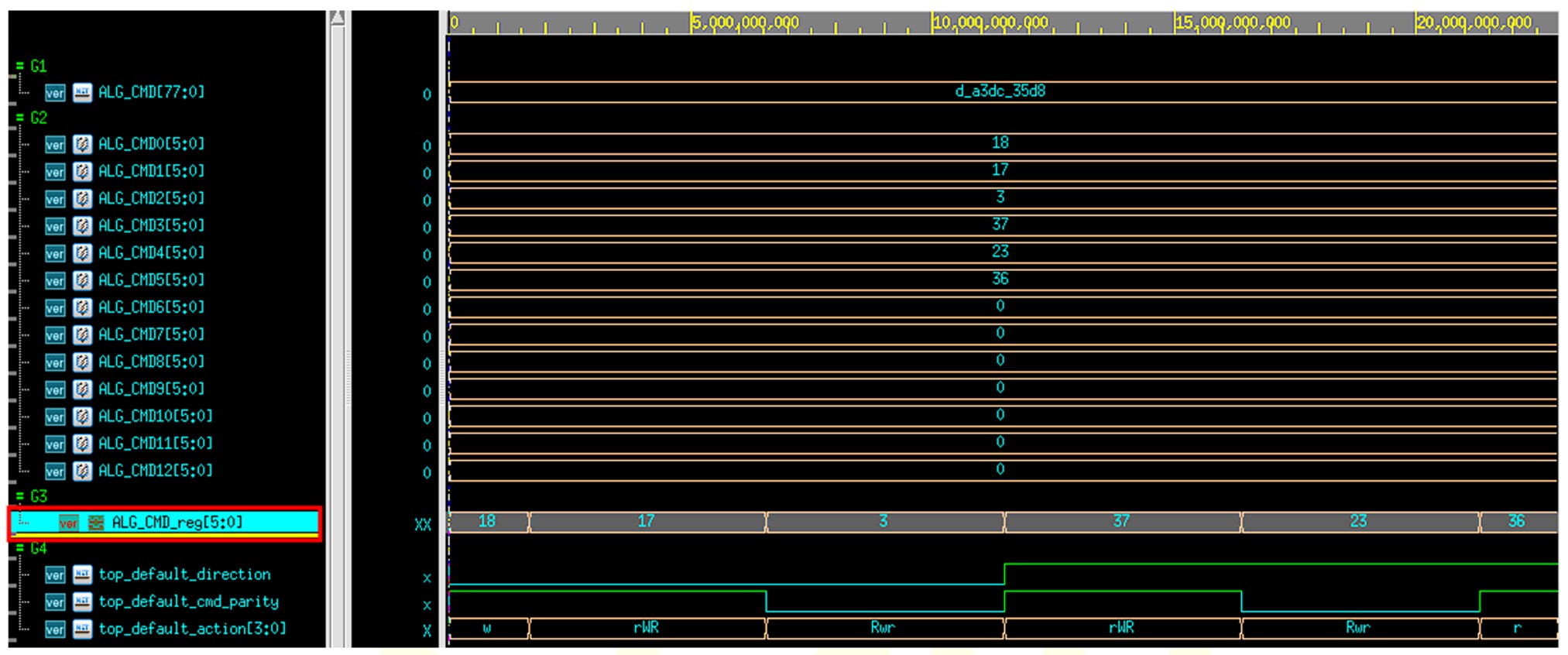

EZ-TEC is a modular architecture based on iSTART-TEK’s U.S. patent, “METHOD FOR GENERATING A MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT.” EZ-TEC allows users to adjust the sequence of algorithm elements during CP testing, such as the W, rWR, and Rwr elements shown in the figure below. Users only need to prepare four elements to combine and create a standard algorithm like March C+.

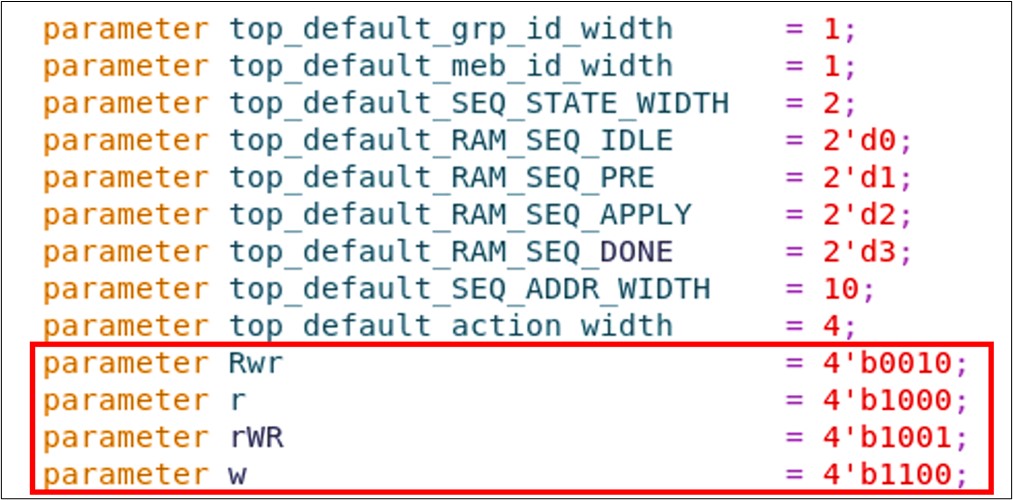

The Combination of Elements and Codes

Each element has a corresponding code, allowing users to create new testing algorithms by combining these codes.

Change Testing Algorithm Behaviors

Users can configure and modify testing algorithm behaviors through external interfaces, such as JTAG or send_command in the testbench.

send_command task

send_command = {PRL_ON, GRP_EN, MEB_ID, BG, ALG_CMD, MEN}

- PRL_ON:Determine to perform parallel testing.

- GRP_EN:Determine the group to be tested (each bit represents one group).

- MEB_ID:Determine the Memory ID to be tested (0 represents testing all memories).

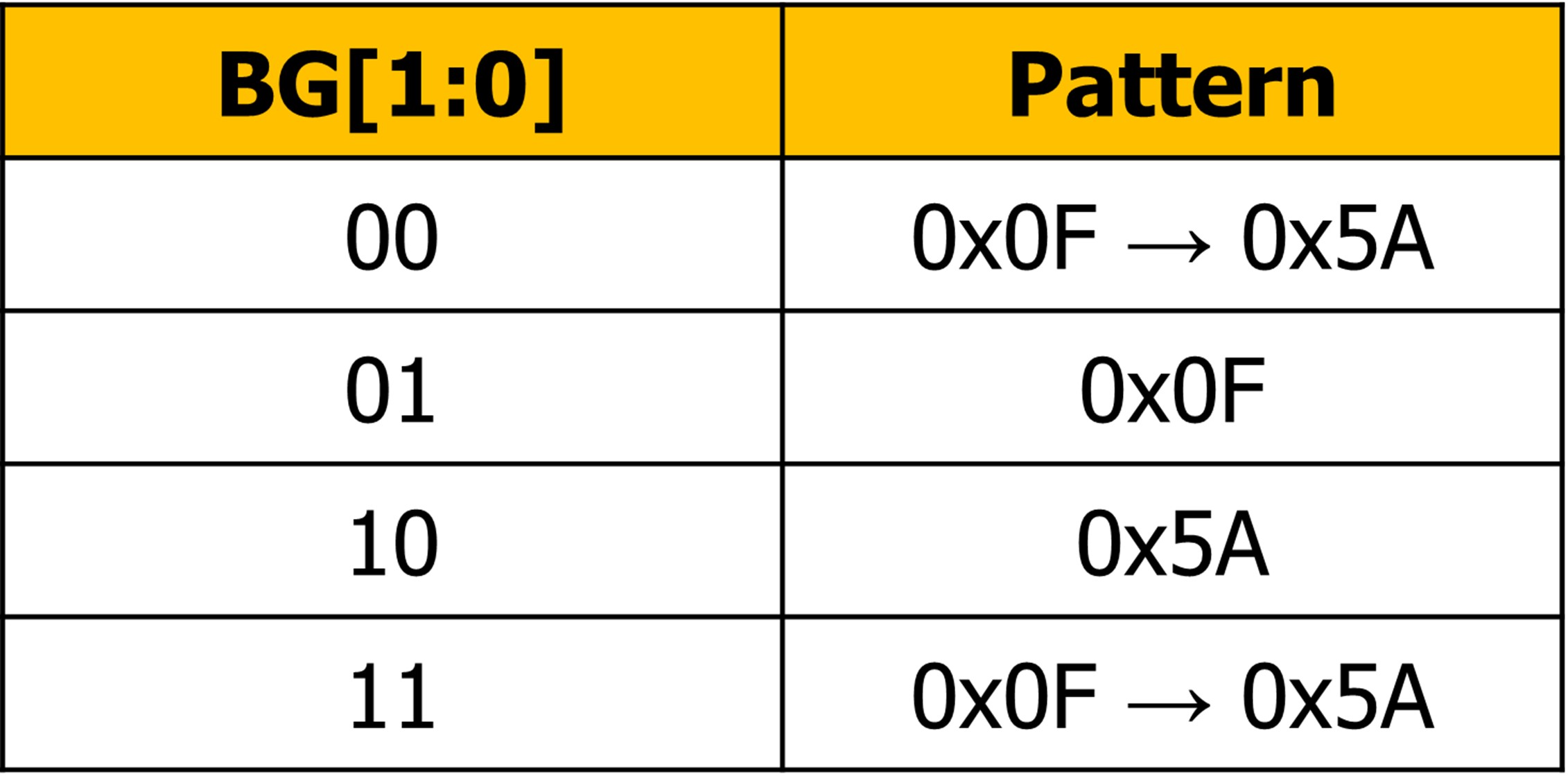

- BG:Specify the background sequence for testing.

- ALG_CMD = {ALG_CMD12, ALG_CMD11, … , ALG_CMD1, ALG_CMD0}

- MEN:Initiate the Memory BIST testing

ALG_CMD

- ALG_CMD0~12 = {direction, cmd_parity, action}

- direction:Specifies the order of address testing. 0 indicates ascending order, while 1 indicates descending order.

- cmd_parity:Determines the background for the first read/write operation of each element. 1 represents “a”, while 0 represents “b”.

- action:Obtains the value represented by each element from the MBIST code.

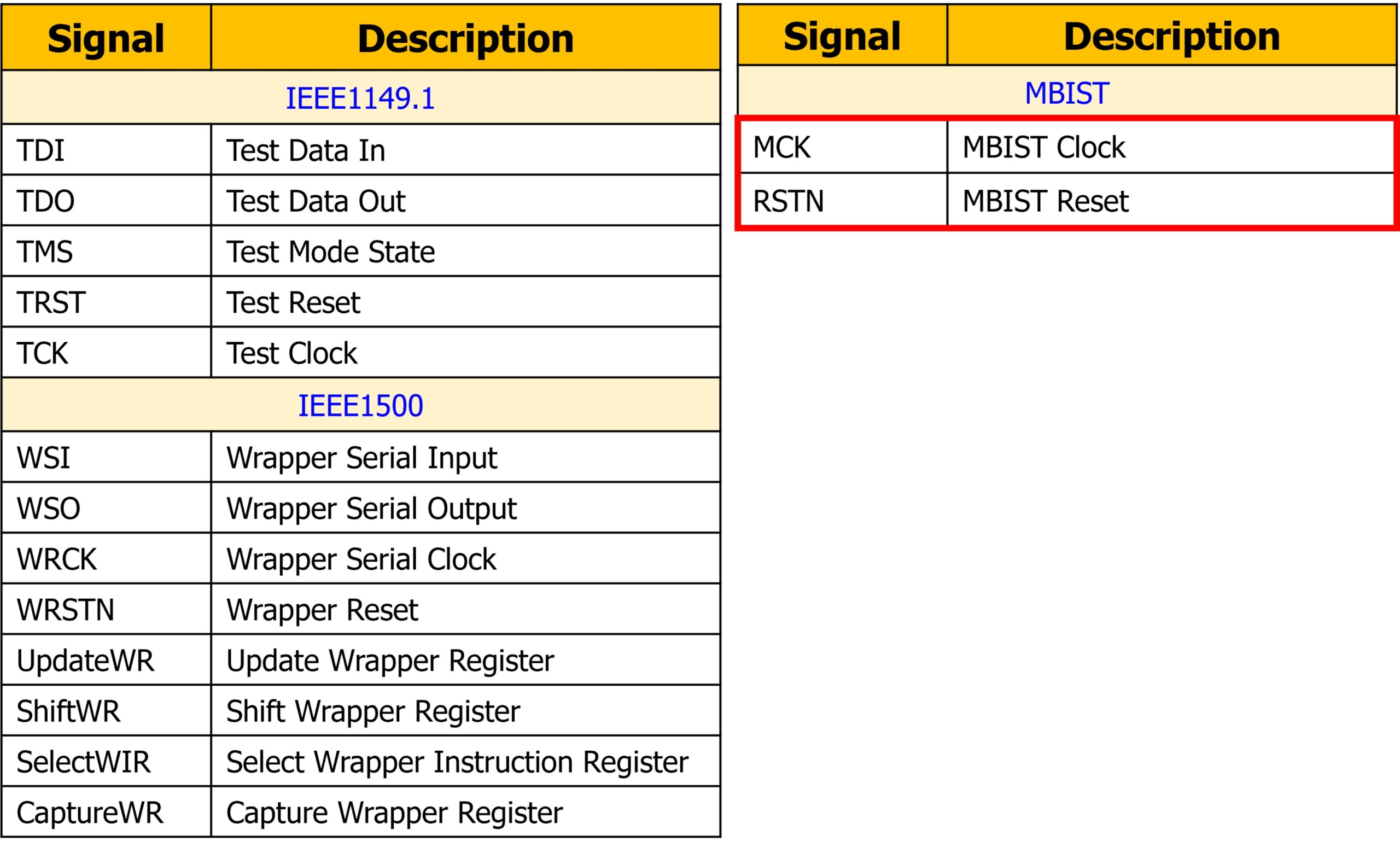

EZ-TEC Interface Pins

EZ-TEC supports IEEE1149.1 and IEEE1500 interfaces. The MCK (Memory BIST Clock) is the clock signal for MBIST, and RSTN (Memory BIST Reset) is the reset signal for MBIST.

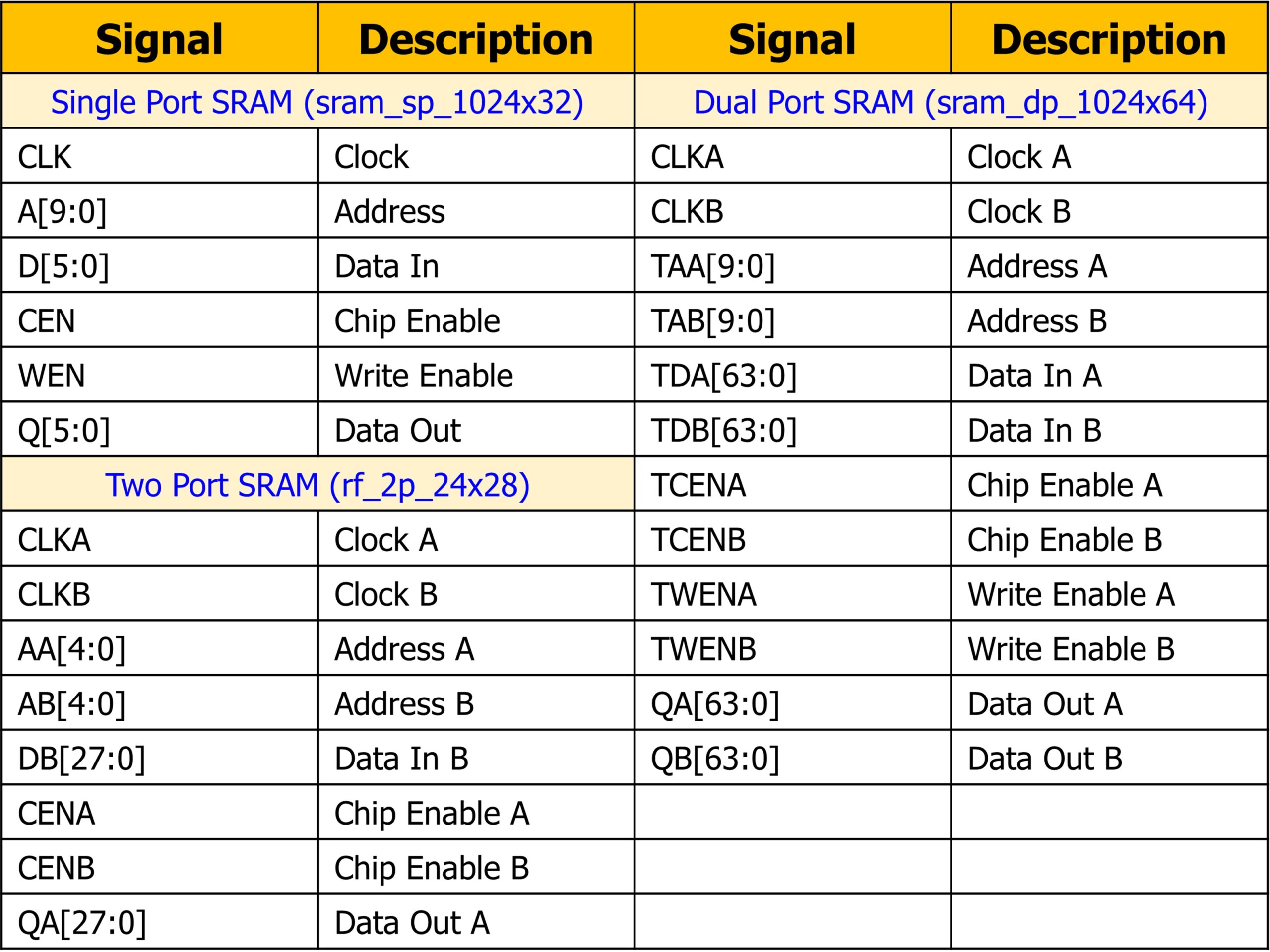

The Corresponding Interfaces of Different SRAM Types

EZ-TEC Waveform

ALG_CMD collects the signals from 0 to 12. After shifting by 6 bits, the result is stored in ALG_CMD_reg, and the March C+ algorithm is then executed sequentially.

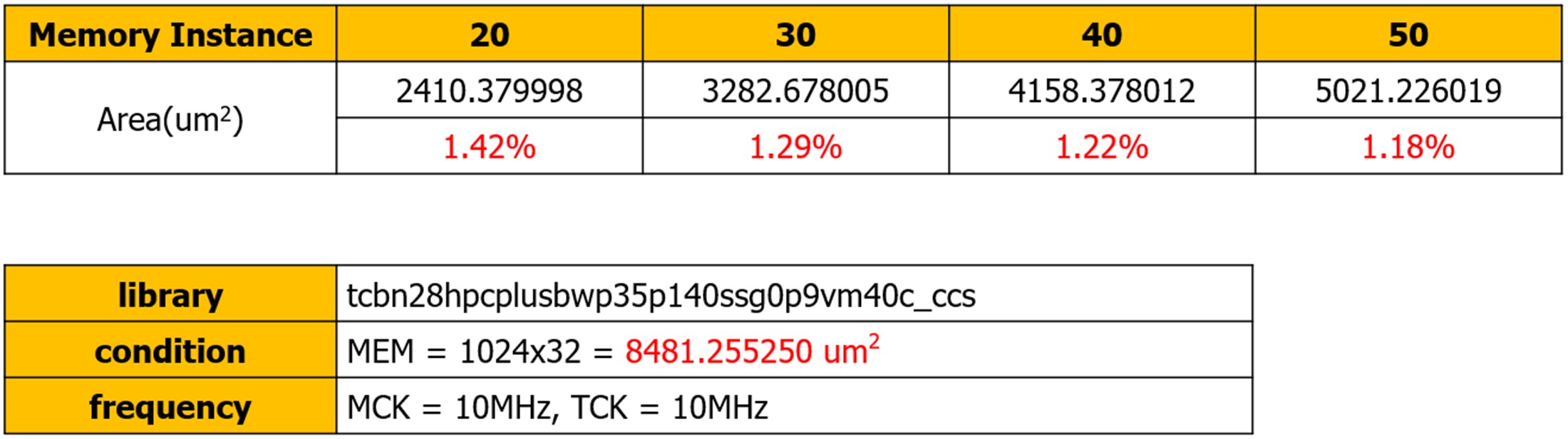

EZ-TEC Area Proportion

iSTART-TEK’s EZ-TEC adopts the concept of Hardware Sharing, so as the number of SRAM units increases, the area growth rate becomes smaller.

After chip production, users can adjust algorithm behaviors through EZ-TEC at the CP testing stage. Whether without changing the original MBIST architecture or adopting other providers’ MBIST solutions, iSTART-TEK’s EZ-TEC IP can rearrange and develop new testing algorithms, thereby increasing chip yield and reducing DPPM.