全球汽车朝向智能化与电动化,使车用电子更重视芯片的可靠度测试及安全性功能,以期达到 AEC-Q100 的规范,进而打进车用市场。芯测科技的 START™ v3 除了提供丰富的内存测试功能与高效率的内存修复技术,还提供专属的定制化车用电子功能,如: POT 2.0 (Power_On Test), ECC (Error-Correcting-Code), UDA(User Defined Algorithm)等功能。让芯片开发商可以根据芯片的应用,精准检测出有内存缺陷的车用电子芯片,提高行车安全。

一、 POT 2.0 (Power_On Test)

1.功能介绍:POT 2.0 (Power_On Test)在电子产品里是非常重要的功能,尤其在车用与安全性相关的电子产品。能确保硬件电路在上电后进行内存检测,并验证行为正确性。芯测科技开发了具有内存测试与修复功能的 POT 2.0,加入 START™︎ v3 工具中,可以让使用者方便在设计里加入内存 POT 功能的电路,并提供下列几种启动方式:

- ROM:将测试命令(Command)存入 ROM。

- RTL:将测试命令存入由 RTL 描述的 ROM。

- Basic:提供 host_MEN 信号,进行内存测试。

- CPU:可以透过 CPU 下达测试指令来控制 BIST 电路。

在应用上也能加入 LATCH_GO 诊断功能,以一颗内存对应一位的形式进行内存错误编号标记,让用户快速了解内存发生错误的位置。而 Error Injection 的功能,能在电路 Test Pattern Generator 中植入用于验证 BIST 电路正确性的错误信息,能大幅增加 BIST 电路可靠度。此外,使用 POT 2.0 时,如检测出新的内存错误,皆能对错误点进行内存修复。

2.使用方式:

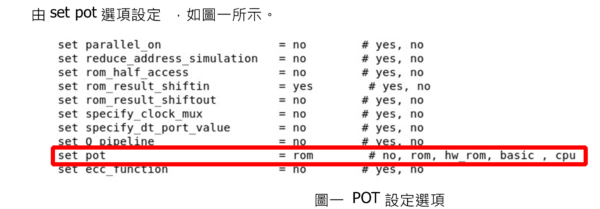

设定 START™ v3 ( BFL ):

- set pot = rom or set pot =hw_rom

设定 pot 选项为“rom”,测试命令将被存入 ROM;设定 pot 选项为“hw_rom”,会将测试命令存入由 RTL 描述的 ROM,又称为 Hardwired ROM。最后完成 BFL 与 BII 流程,产生相对应之电路与脚位以供使用。

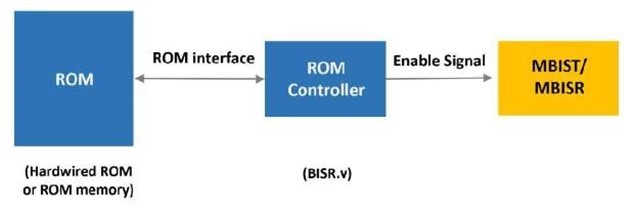

POT 的模块图,主要分为三个模块,分别为 ROM 内存/Hardwired ROM, ROM Controller 和MBIST/MBISR,如图二所示。

首先 ROM Controller 接收到执行 POT 功能后,会读取存放在 ROM 内存/Hardwired ROM 的测试命令,接着发送控制讯号到 MBIST,开始进行内存的测试,若检测到内存错误,MBISR 则会自动执行修复流程。

图二 POT 模块图

图二 POT 模块图

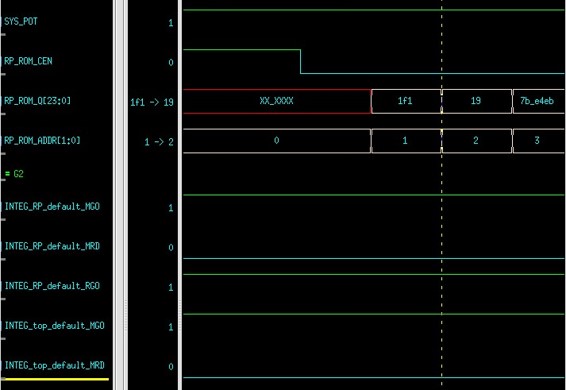

执行POT 功能相关讯号的波形图,SYS_POT 为POT 的始能讯号,此讯号启动后,ROM Controller 会到ROM 内存/Hardwired ROM 进行读取测试指令,并开始内存测试与修复,可由MGO,MRD,RGO讯号得知测试结果,如图三所示。

图三 POT 相关讯号波形图

POT= “rom” 或 “hw_rom” 的 MBIST/MBISR 的讯号线如图四所示。

| Name | Direction | Width | Description |

| SYS_READY | input | 1 | The system boot is ready to enable BISR logics(hard repair only)

“1’b1”: Ready to load data from NVM storage) |

| SYS_POT | input | 1 | Enable Power on test (normal function test only) |

| BOOT_CFG_DONE | output | 1 | The shifting of configuration data is completed (hard repair only).

“1’b1”: the scan is completed “1’b0”: the scan is progressing |

| RCK | input | 1 | The clock signal for storage device, BISR logics and configuration buffer |

| RRST | input | 1 | The reset signal for storage device, BISR logics and configuration buffer |

| MRD | output | 1 | Indicates if the test is ended or not.0: The test is uncompleted.

1: The test is ended. |

| MGO | output | 1 | Indicates if the test is failed or not.0: The test is failed.

1: The test is passed. |

| RGO | output | 1 |

图四 hw_rom 与 rom 的 MBIST/MBISR 讯号

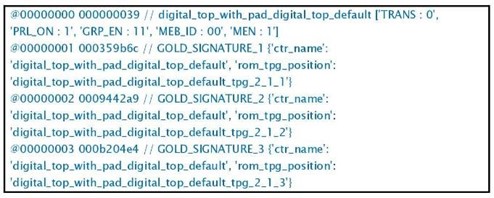

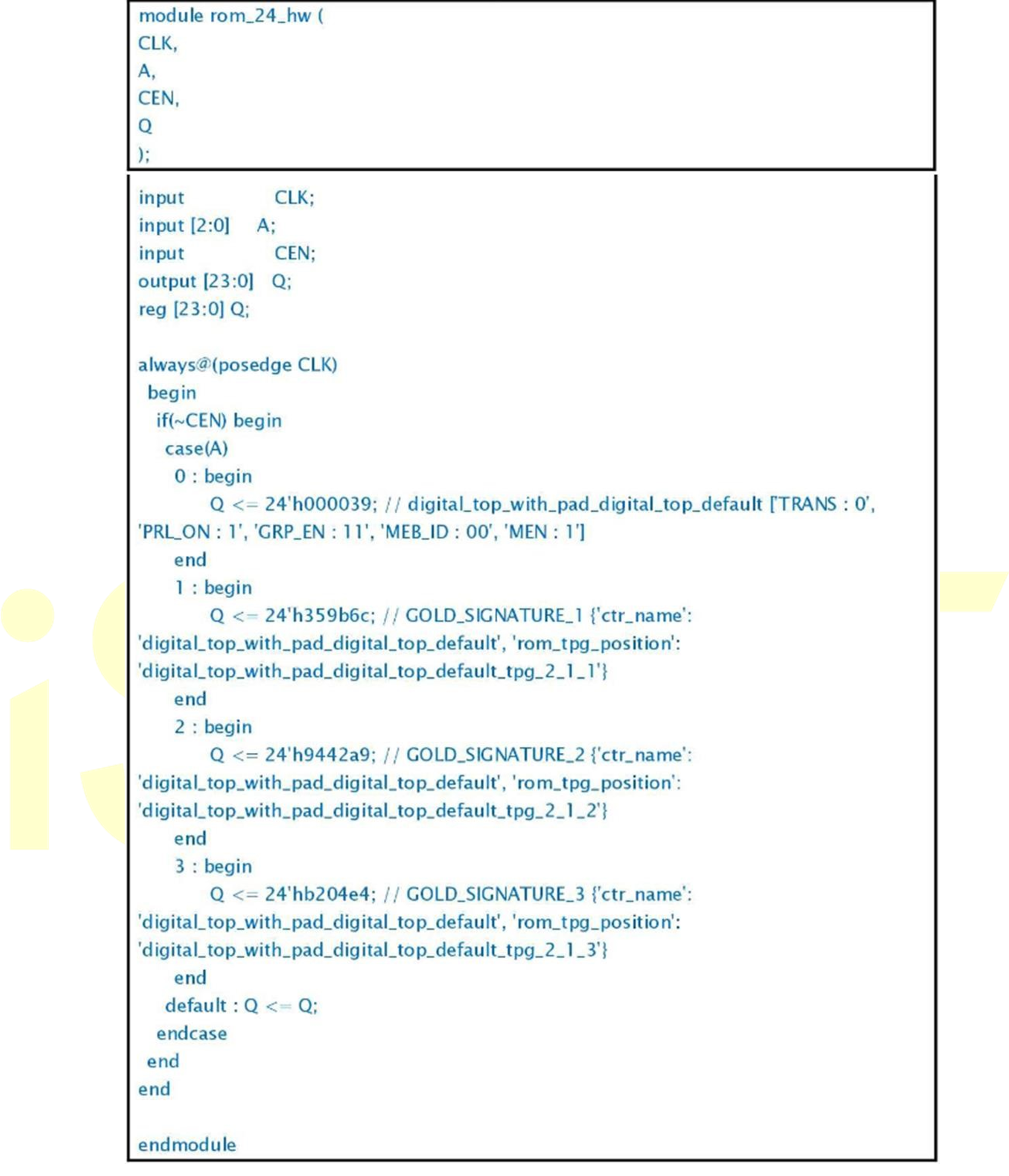

最后产出存入 ROM 之测试命令的 Verilog 档案,根据用户设计的 BIST 功能,产生相应的命令,如图五所示。Hardwired ROM 之 Verilog 程序范例,将测试命令存入由 RTL 描述的 ROM,如图六所示。

图五 存入 ROM 测试命令

图五 存入 ROM 测试命令

图六 Hardwired ROM 的 Verilog 程序

ii. set pot = basic

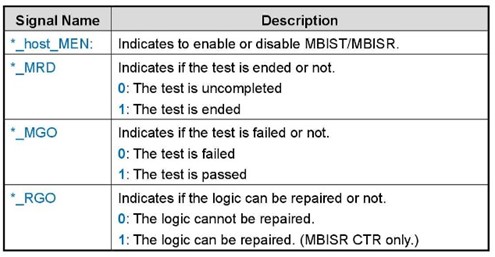

设定 pot 选项为 “basic” 将产生 host_MEN 信号线,供用户启动内存测试,并可由 MGO, MRD, RGO 讯号得知测试结果, “basic” 选项产生之讯号列表,如图七所示。

图七 basic 选项的 MBIST/MBISR 讯号

iii. set pot = cpu

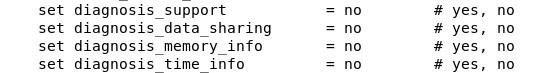

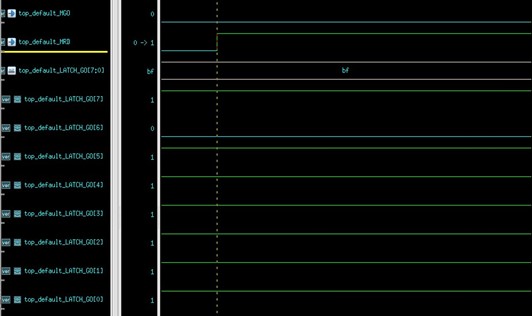

设定 pot 选项为 “cpu”,可令用户直接进行 BIST 电路的控制,并可由调整.bfl 档案之设定,如图八所示,增加额外功能,例如 diagnosis_memory_info 功能可新增 LATCH_GO 讯号,令用户得以快速了解发生错误之内存编号。编号六之内存发生错误,如图九所示。

图八 BFL 上 Latch_GO 设定

图九 Latch_GO 波形图

二、 ECC (Error-Correcting-Code)

1.功能介绍:

ECC (Error-Correcting-Code)是指在传输时间允许侦测并校正错误的一种编码方法,在接收端藉由已编码数据侦测并校正传输错误,可应用于许多数据传递与数据保存的操作。在内存方面,ECC 能使用电路方法检查储存在内存中的数据是否正确。

不论是应用在汽车、工业、医疗及通讯等领域,都可能因内存失效,导致严重后果,而 ECC 的功能,能提高芯片运行时的稳定性和可靠性。

芯测科技提供 ECC 的功能,让用户在内存增加 ECC 功能,使用上可帮助使用者做到 2bits 的侦测, 及 1bit 的修正,而使用时须由内存提供 ECC 使用奇偶校验(Parity Check)的空间,来重建校正的数据,须提供的空间为 2Parity-1> Parity + Data bit,例如内存数据长度为 22bits 时,使用 6bits 的 ECC 空间来检测 16bit 的数据。

2.使用方式:

设定 STARTTM v3 ( BFL ):

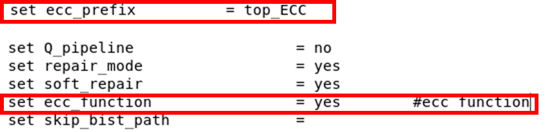

由 set ecc_function 选项设定启动方式以及 set ecc_prefix 设定 ecc 名称,如图十所示。

图十ECC设定选项

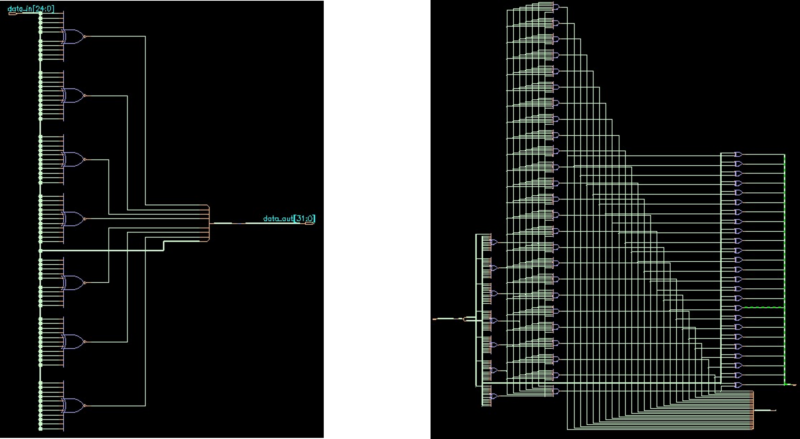

执行完 BFL 与 BII 流程后,产生 ECC 功能的编码与译码电路,如图十一、图十二所示。

图十一 encoder 电路 图十二 decoder 电路

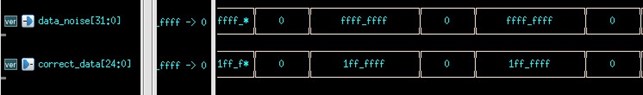

ECC 波形图,data_noise 为内存的 data 与编码过的校验值,透过译码后,得知 correct data,并可进行 data 修正,如图十三所示。

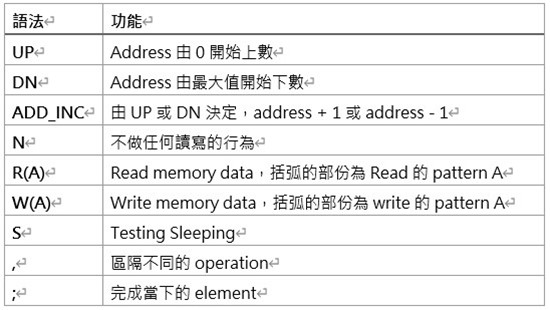

三、UDA (User Defined Algorithm)

1.UDA 功能介绍:

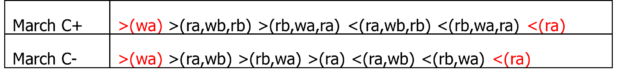

随着科技的演进,新开发的先进制程内存搭配现有常见的算法,会花费较长的测试时间,并且会有重复测试图像的行为。例如:使用者若同时选择 March C+(14N)与 March C–(11N)的算法,测试时间需要 25N。

芯测科技研发了用户自定义算法功能 UDA (User Defined Algorithm) 可以自行编辑算法,将重复的元素 (element)去除,去除后测试时间即可缩短成 23N。

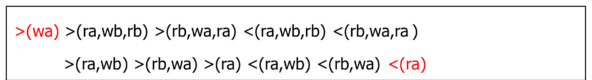

UDA 以组件的形式表达,可透过组件进行重新排列组合,任意产生出新的算法,如图十四所示。

UDA 以组件的形式表达,可透过组件进行重新排列组合,任意产生出新的算法,如图十四所示。

图十四 以组件的形式表达

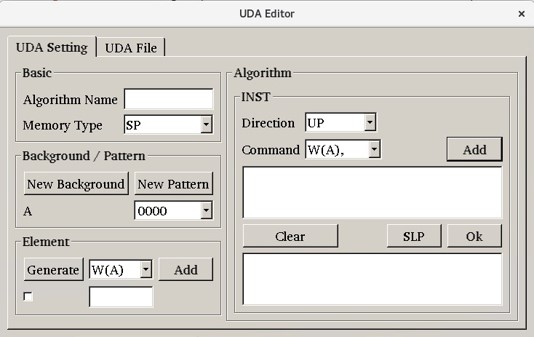

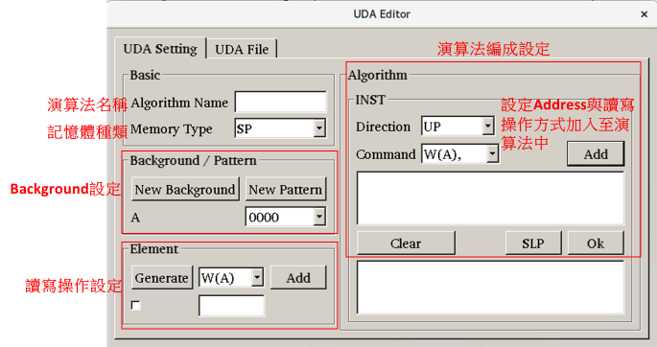

图形用户界面 (GUI),友好接口让用户能快速上手,如图十五所示。

图十五 UDA 图形化操作画面

2. 使用方式:

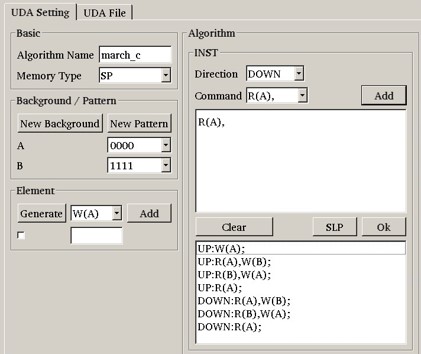

透过 UDA 图形化操作接口,可快速的设定元素,下图十六为图形化操作接口的各项区块简介,能简易的设定测试图像、读写操作方式及地址上下数,完成后产生出算法。

图十六 图形化操作接口简介

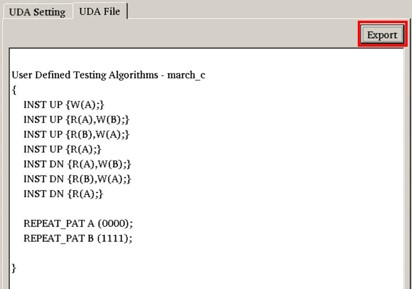

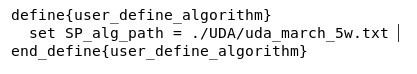

举例一个 March C 的算法,利用图形化操作接口,完成算法的设定后,点选 UDA File 可看到算法设定的结果,并按下 Export,即可将此算法输出成.txt 檔。最后在.bfl 配置文件中,设定上述.txt 文件之路径,完成后即可产生出此算法的 BIST 电路,如图十七、十八、十九所示。

图十七 March C 算法设定

图十八 算法输出

图十九 UDA 档案设定