随着先进制程的应用越来越广泛,物联网(IoT, Internet of Things)芯片、高效能运算(HPC, High Performance Computing)芯片、人工智能(AI, Artificial Intelligence)芯片、边缘运算(Edge computing)芯片与图像处理(ISP, Image Signal Processing)芯片等,都需要使用更先进制程。在先进制程与上述各类应用需求的提升下,使用 SRAM(SRAM, Static Random Access Memory)来储存复杂的程序的情况越来越多。如何精准找出内存缺陷,降低 DPPM(DPPM, Defect Parts Per Million)相当重要。

过去要设计一个内存测试算法,需要芯片设计工程师,根据芯片应用的特性、芯片测试后的诊断报告和制程,选择适当的算法。通常芯片设计工程师就会选择最基本的 March C 或是 March C-做为芯片量产测试的算法。

近期,制程的演进快速,让过去使用成熟制程的芯片开发商,必须选择较为先进的制程,随之而来的就是内存测试算法的改变,因为过去使用的内存测试算法,已经无法精准的检测出在较为先进制程下的内存缺陷的型态(Memory defect type),造成 DPPM 提高。

然而,过去芯片设计工程师只能利用土法炼钢的方式,在 RTL(Register-Transfer Level)阶段,根据芯片测试后的诊断报告或是制程,选择更适当的内存测试算法,通常伴随着就是芯片开发时间的拉长,因为芯片设计工程师无法有效率且精准的设计出更为适当的内存测试算法。如何快速且有效率的完成内存测试算法的变动呢?

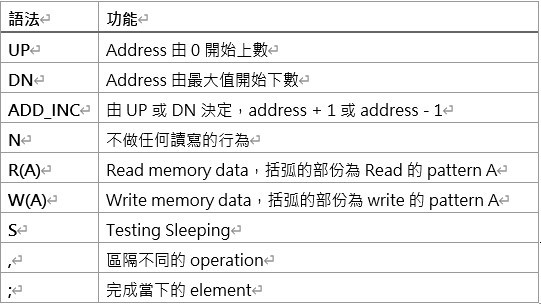

芯测科技推出全世界第一套完全以图形接口为主(GUI-Based)的用户自定义算法(UDA, User Defined Algorithm)微架构。芯测科技将内存测试算法,以组件(Component)的形式表达,如表一,然后利用组件间的『重新排列组合』,形成新的内存测试算法。

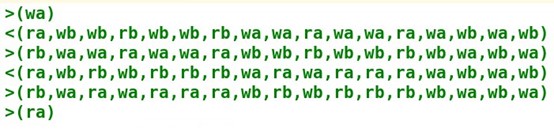

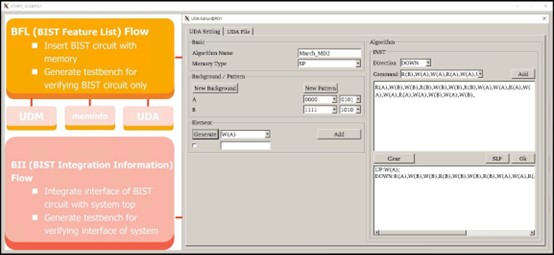

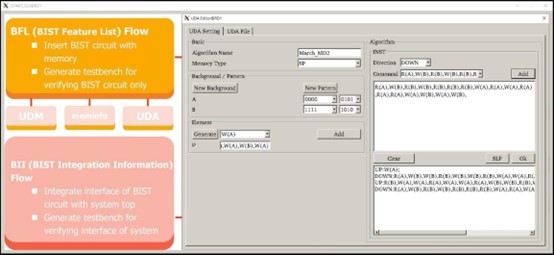

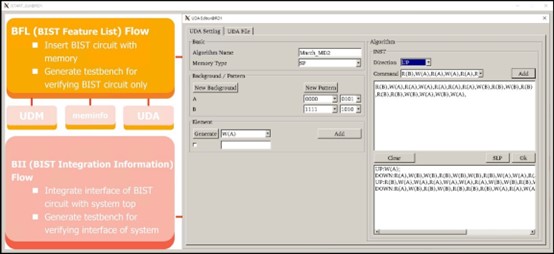

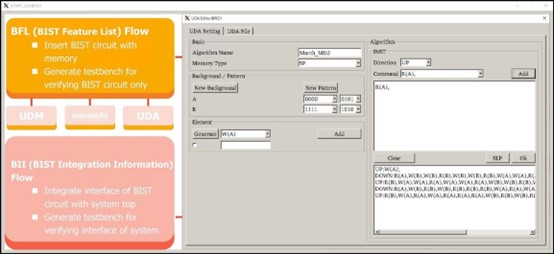

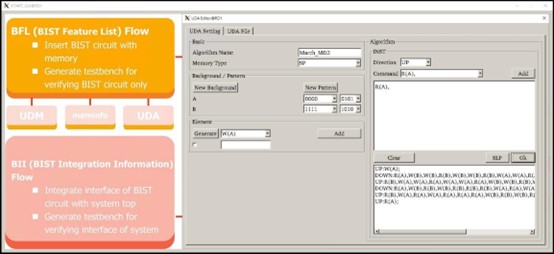

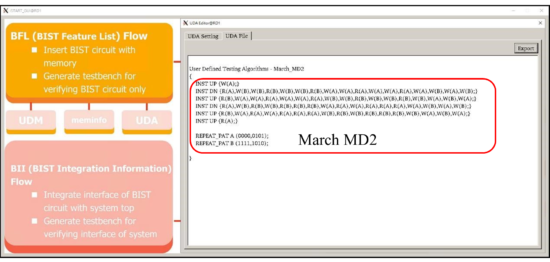

如此一来,任何内存测试算法都可以利用 UDA 在几分钟内产生,大幅缩短芯片设计者开发内存测试算法的时间,也可以让芯片设计者根据内存缺陷的信息,快速的产生『专用的』内存测试算法。此外,透够组件化的架构,UDA 产生的内存测试算法的电路面积也相当精简。以下为产生一个复杂度为 70N 的内存测试算法 March MD2(如图一)的操作说明:

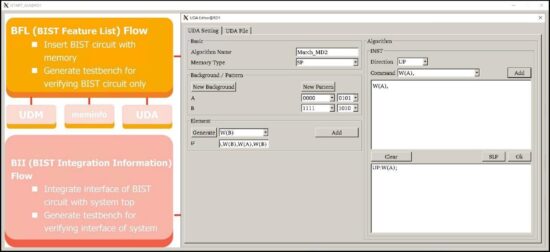

一、透过 GUI 选择 UDA 的使用,如图二。

图二

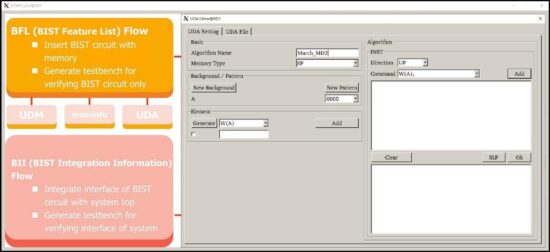

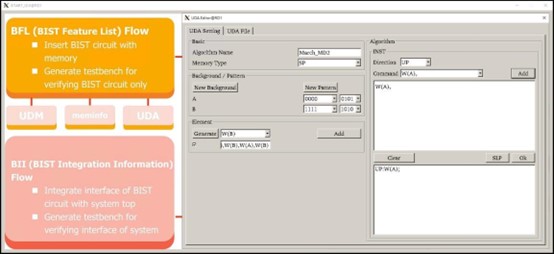

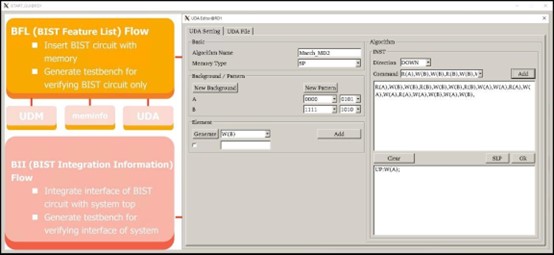

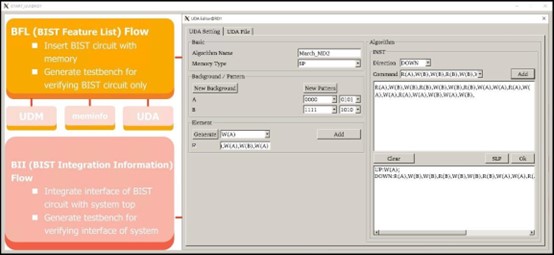

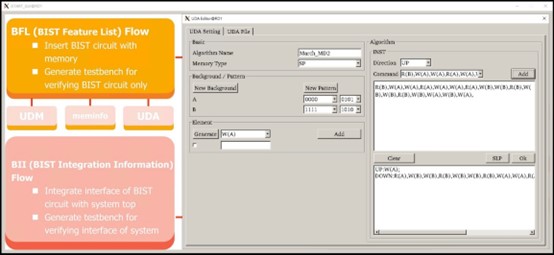

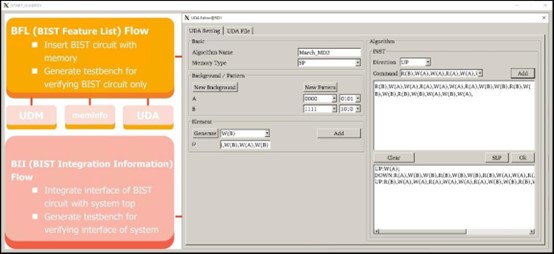

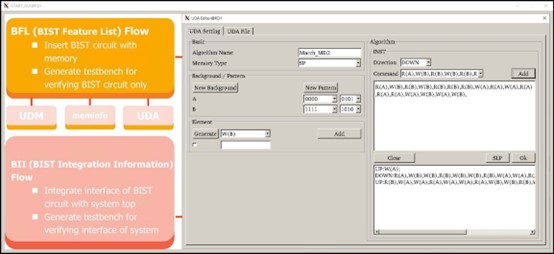

二、透过 GUI 根据 March MD2 的算法依序完成内存测试算法的实现,如图三、图四、图五、图六、图七、图八、图九、图十、图十一、图十二、图十三、图十四、图十五、图十六。

图三

图三

图四

图五

图六

图七

图八

图九

图十

图十一

图十二

图十三

图十四

图十五

图十六

过上述几个步骤,芯片设计工程师,可以利用 UDA 微架构设计出复杂度很高的内存测试算法。透过 UDA 的使用,让内存测试算法的设计更具弹性化也更多元。

先进制程的演进带动内存需求的增加,相对的各种内存缺陷的型态也会因应而生,开发出复杂度够高的内存测试算法,才可精准的检测出各类的内存失效情况。

芯测科技的 UDA 微架构,可望为芯片设计者带来快速、省成本且高效能的服务。