最具性价比的內存调适环境:EZ-Debug

在日益蓬勃发展的集成电路产业中,确保集成电路是否符合设计规格和功能已是开发与制造过程中不可或缺的重要环节。在这关键的任务下,IC产业广泛运用自动测试装置(Automatic Test Equipment, ATE)来执行测试工作。然而,过去,在处理小批量或是非量产的芯片测试时,常常仅能藉由使用ATE机台进行,但这却往往伴随需要额外的成本投入以及漫长的测试时间。

而芯测科技(上海芯复瑞)近期研发一款基于计算机平台的JTAG转USB的调适环境: EZ-Debug,可以针对非量产芯片以及开发中的芯片进行快速且高效率的进行测试,不仅可以省下ATE测试的成本,同时还可以及时的知晓结果。

一、EZ-Debug架构

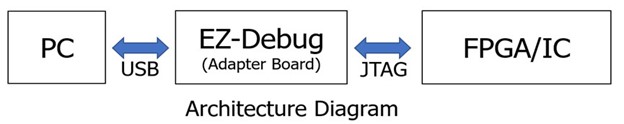

EZ-Debug可以快速且方便进行调适,EZ-Debug主要是透过转接板进行计算机与FPGA/EVB board之间的沟通。转接板与整体工具的规格示意图如下图所示。计算机与转接板是用USB做连接,转接板配合工具会将讯号转换成JTAG,再送给FPGA/EVB board进行调适。

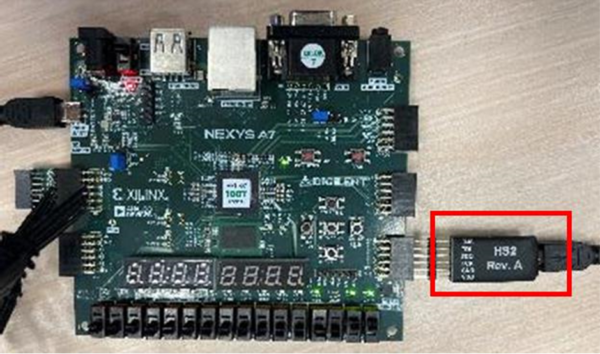

下图为实际使用示意图,红色框起来的是转接板,转接板右侧是FPGA,左侧是计算机端,此FPGA是用于模拟非量产chip或是开发中的chip。

二、EZ-Debug实际使用

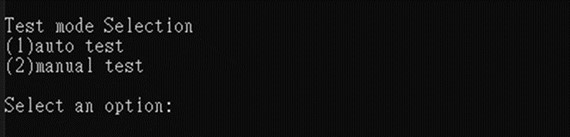

在计算机端安装完EZ-Debug以及转接版的驱动程序后,即可开始使用调适。EZ-Debug提供两种测试模式:(1)auto test、(2)manual test。

1.EZ-Debug测试模式 – auto test

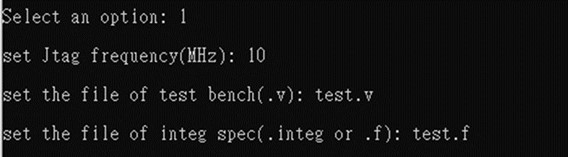

使用时需设定JTAG的频率、STARTTM v3产生的test bench file以及STARTTM v3产生的integ spec file,设定完成后EZ-Debug即会自动进行BIST的测试,Jtag frequency : JTAG在FPGA/EVB的使用频率。

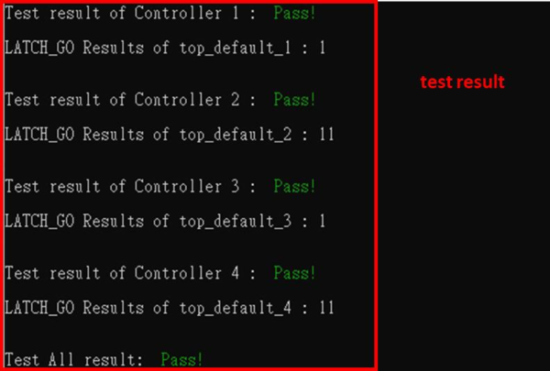

file of test bench : START在BII时产生可提供模拟需要的档案(ex: integ_tb.v) file of integ spec : START在BFL时产生BII整合需要的档案(ex:[ctr_name]_spec.integ) 进行auto test时,EZ-Debug会对design里的每一个controller进行BIST的测试,并将测试结果显示在屏幕上,若所insert的BIST电路有支持LATCH_GO功能,EZ-Debug同样也会一并显示LATCH_GO的结果。

当测试结果是PASS时,则会显示Test Pass!并且LATCH_GO的结果为 ‘1’。

[Test Pass]

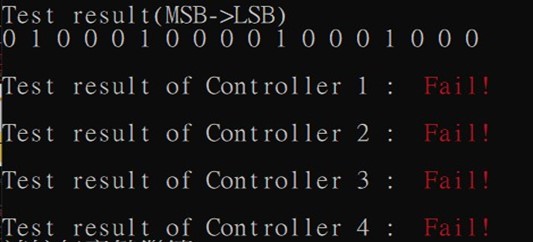

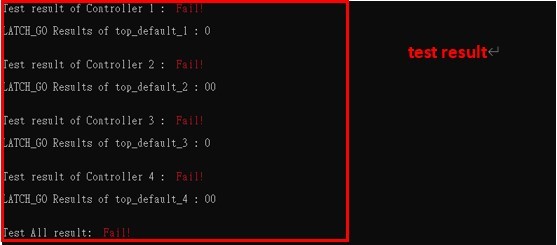

而测试结果为FAIL时,则会显示Test Fail!并且LATCH_GO的结果为 ‘0’。

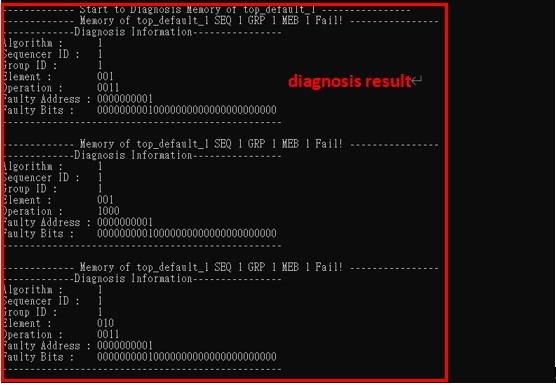

若insert的BIST电路有支持Diagnosis功能时,EZ-Debug会进行Diagnosis的测试,并且将Diagnosis测试完成的信息显示在屏幕上。

[Test Fail]

2.EZ-Debug测试模式 – manual test

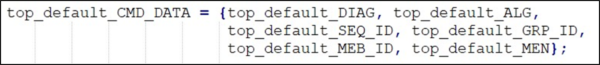

首先可以要参阅做完整合的INTEG testbench 中bist_testing这个task,在这个 task中我们可以找到下图的CMD_DATA信息,依照下图信息即可填写设定input binary value去使用JTAG的TDI做send_command,即可开始测试。

JTAG的TDO会产出capture_commad,而capture_commad可参考下图INTEG testbench中的test_result的讯号排列,即可解读capture_commad的内容。

![]()

讯号解释:

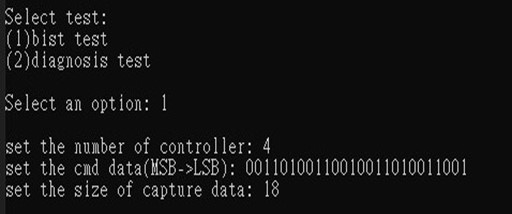

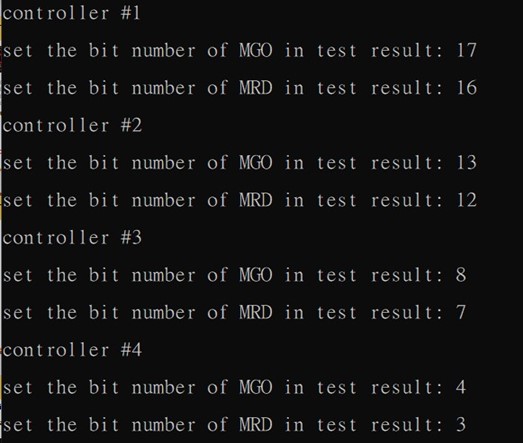

[ctr_name]_MGO : 为BIST测试结果,当BIST测试fail时,为0。 [ctr_name]_MRD : 为BIST测试完成时,会为1。 [ctr_name]_SRD : 当Diagnosis Data已准备好时,会为1,即可进行capture Diagnosis Data。 [ctr_name]_LATCH_GO:此讯号的width是依照START所产出的meminfo檔中的 memory数量而定,当LATCH_GO的每个讯号从1变到0时,代表此颗memory测试fail。使用时输入controller的个数、测试的command,capture result的长度,以及MGO/MGD的bit number,EZ-Debug即会进行测试,并将测试结果的row-data显示在屏幕上。

[输入测试command]

[输入MGO/MRD bit number]

[测试结果]