EZ-TEC 介紹

EZ-TEC IP 能將測試演算法轉化為模組化的元件。使用者可以透過元件的靈活組合,創造出與傳統演算法截然不同的測試演算法,進而偵測到先進製程下SRAM的記憶體缺陷。在晶片生產後,使用者依然可以在CP階段調整演算法的行為,加以提高晶片的良率,減少DPPM。無論是在不改變原始BIST架構的情況下,還是採用其他廠商的MBIST方案,EZ-TEC都能針對重要或面積較大的SRAM重新排列組合出新的測試演算法。

EZ-TEC 使用流程

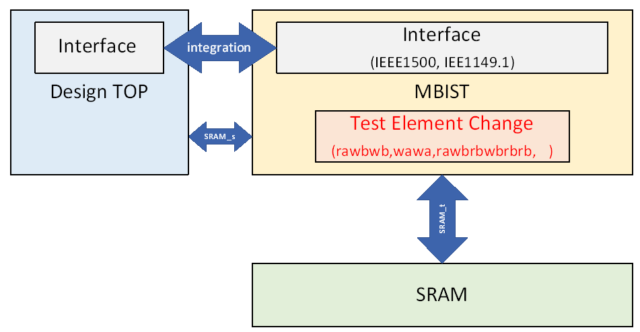

首先是EZ-TEC的架構圖。SRAM_s代表原始SRAM介面,而SRAM_t則是MBIST處理後與SRAM的介面。使用者可以保留原始架構,以IP形式新增電路。

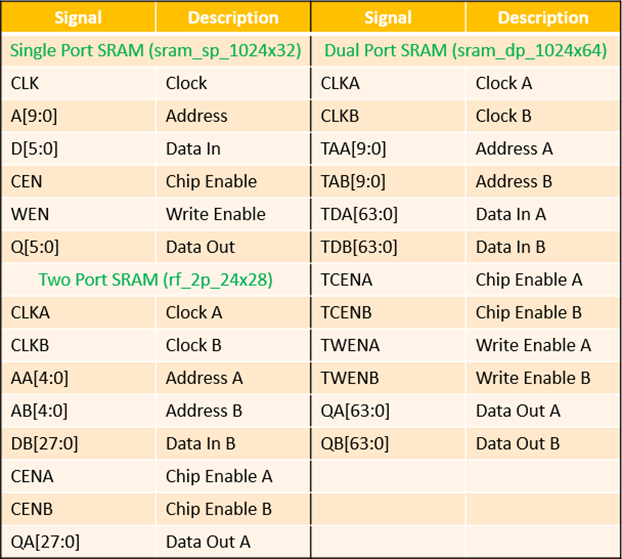

不同SRAM類型對應的介面:

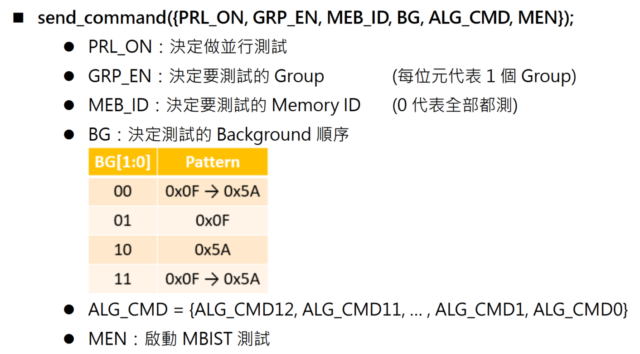

使用者可以透過外部interface,例如JTAG、以及test bench中的send_command來設定及更改測試演算法的行為。

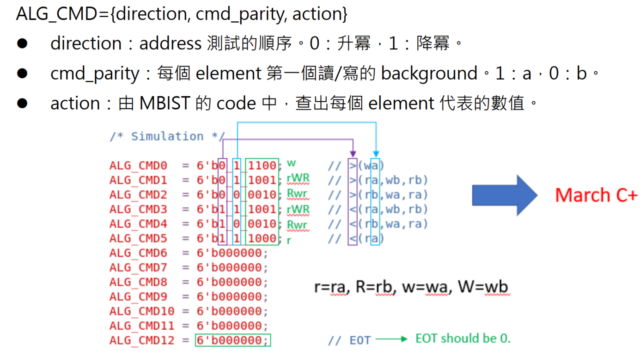

ALG_CMD是由direction、cmd_parity和action所組成。

每個元件都有其相對應的代碼,使用者可以透過代碼組合,排列出新的演算法,如畫面的新演算法行為。

為什麼您需要EZ-TEC?

當使用者在使用晶片時遇到SRAM問題,而原始MBIST電路無法檢測出這些缺陷,這時就可以透過EZ-TEC SRAM IP增加新的測試演算法,藉此提升晶片的良率。此外,EZ-TEC沒有製程上的限制,支援所有先進製程,是提高晶片測試效率的關鍵工具。

2024芯測小學堂