隨著現行晶片的運用越來越多樣化,晶片啟動後即不會在斷電關閉又或者運行中隨機監控晶片自身的安全機制,所以在記憶體的安全性與可靠度也就要求的越來越高,相對的在運行中要如何的做到隨時監控晶片內部記憶體是否有損壞或是否誤重作,從而確保晶片自身的安全變為極為重要。

針對這一點,芯測科技資深硬體研發協理沈永勝表示,確保晶片上的記憶體工作正常,內建自我測試修復技術(Built-In Self-Test/Repair, BIST/BISR)與動態隨機測試(DMT,Dynamic Memory Test)成為晶片實作中,不可或缺的一部分。其作用是通過自我測試修復電路與動態隨機測試,來達到監控晶片自身的安全,增加產品的可靠度。

沈永勝指出,對此,芯測科技(iSTART-TEK Inc.)特別開發「記憶體測試與修復的整合性開發環境(SRAM Built-in Testing And Repairing Technology, START)」,透過可配置性設定,協助使用者經過簡單的設定,即可快速的產生記憶體測試修復與動態隨機測試電路,以硬體共享的方式,減少產生的測試電路面積,大幅降低測試與人力成本及縮短量產時程,並提升晶片良率以及達到晶片隨時監控自身的安全,增加整個產品的競爭力。

至於技術上要如何達成,沈永勝以圖文說明如下:

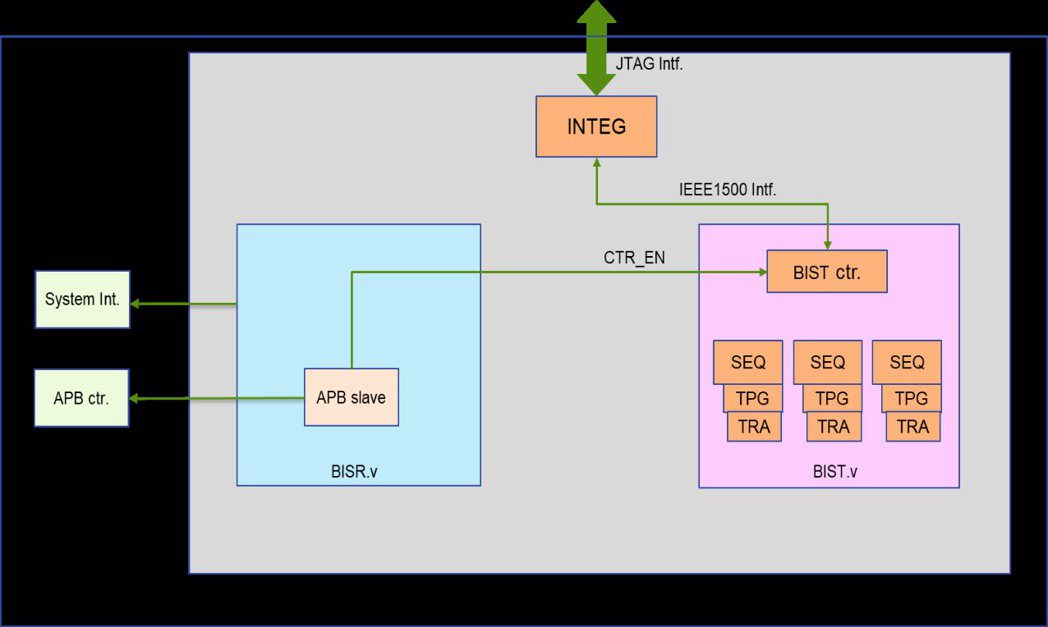

1.DMT Soft-Repair架構圖:此下方方塊圖為DMT Soft-Repair架構圖,右下方塊圖為內建自我測試修復電路(Built-In Self-Test/Repair, BIST/BISR)、左下方塊圖為動態隨機測試電路(DMT)、中間方塊圖為IEEE1149.1接口。

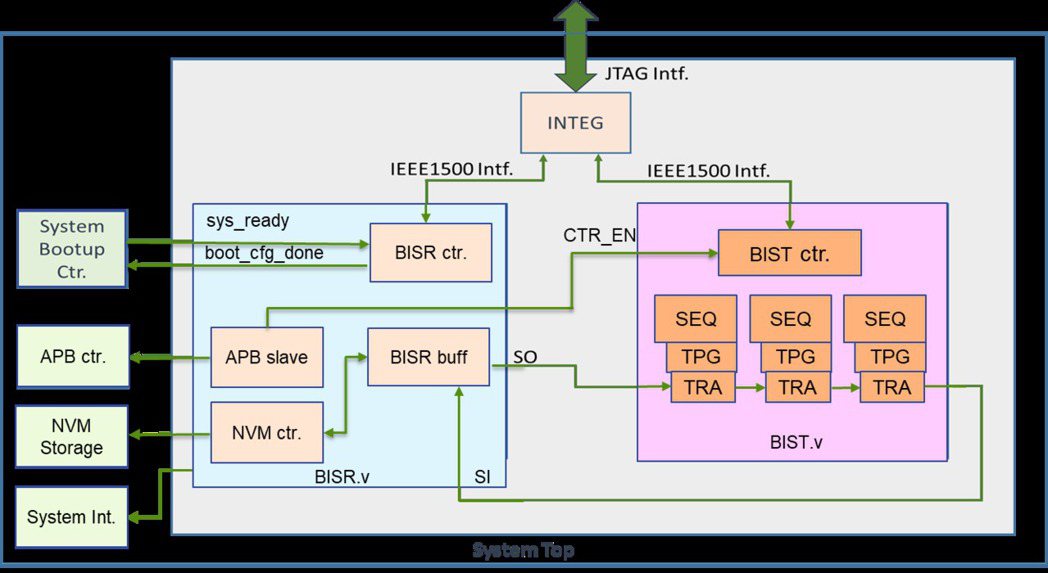

2.DMT Hard-Repair架構圖:此下方方塊圖為DMT Hard-Repair架構圖,右下方塊圖為內建自我測試修復電路(Built-In Self-Test/Repair, BIST/BISR)、左下方塊圖為動態隨機測試電路(DMT)與Hard-Repair控制電路、中間方塊圖為IEEE1149.1接口。

3.DMT Soft-Repair與DMT Hard-Repair特徵

• INTEG

◦ 用於將IEEE1500接口轉為IEEE1149.1接口

• BIST.v

◦ BIST ctr. : 用於控制整個測試流程核心

◦ SEQ : 測試sequence addr和測試element的順序

◦ TPG : 測試pattrern產生器

◦ TRA : 測試redundancy分析器

• BISR.v

◦ NVM ctr. : NVM storage的控制器

◦ BISR buff : NVM storage和TRA之間修復資訊傳輸的橋樑

◦ BISR ctr. : 用於控制整個修復流程的核心

◦ APB slave : 動態隨機測試的接口

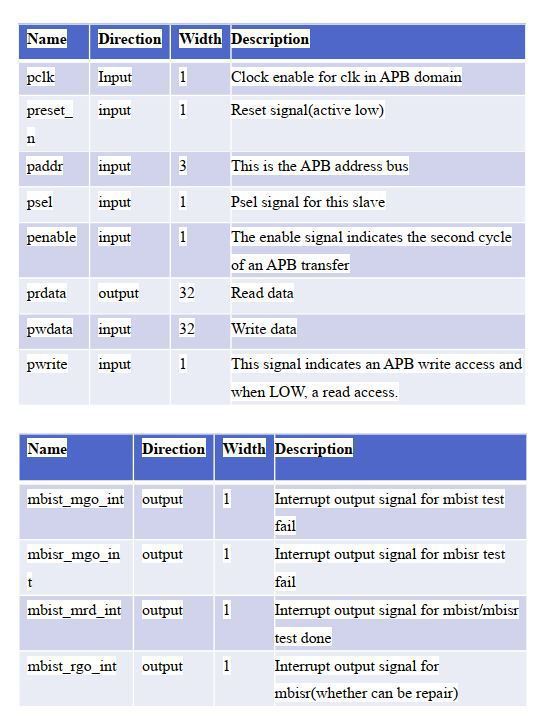

4.APB Interface與系統Interrupt訊號

下方表格所描述為AMBA Standard APB與系統中斷接口訊號

縱上所述,沈永勝表示,鑒於現行晶片運用越來越多樣化,晶片應用於長時間運行又或者運行中隨機監控晶片自身的安全機制的運用越來越多,相對的在運行中要如何的做到隨時監控晶片內部記憶體是否有損壞或是否誤重作,從而確保晶片自身的安全變為極為重要。

沈永勝說,由芯測科技特別開發「記憶體測試與修復的整合性開發環境(SRAM Built-in Testing And Repairing Technology, START)」,具有操作簡單快速上手等特性,卻提供完整的機台測試pattern及合成驗證的script去滿足各式各樣的晶片開發,以此大幅降低測試與人力成本及縮短量產時程,增加整個產品的競爭力。

新聞來源 : https://money.udn.com/money/story/5635/5433129?from=edn_search_result