科技發展日新月異,傳統的演算法在晶片下線後的CP測試(Chip Probe Test,裸晶測試)和FT測試(Final Test,最終測試)階段發現問題時,是無法修改測試演算法的行為。芯測科技所開發的TEC (Test Element Change)功能,以GUI (圖形化操作介面)模式,將記憶體測試演算法的行為元素化,藉由元素的重新排列組合,產生新型態的測試演算法,藉此改變CP測試和FT測試的動態調整及元素重組。即使客戶未採用芯測科技的MBIST電路,也能保留原始的BIST架構,並以IP形式插入原始電路,為客戶在應用上帶來極大的便利性與彈性。

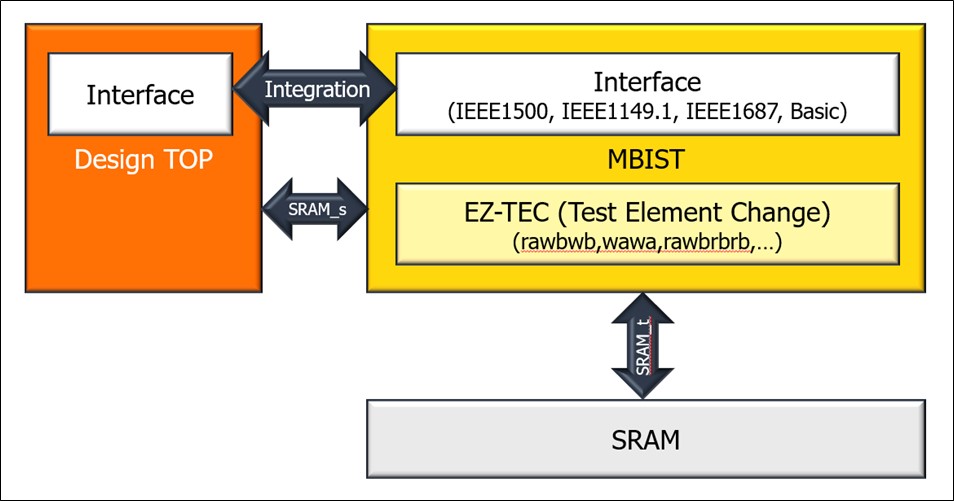

EZ-TEC架構圖

EZ-TEC能夠獨立於任何特定的記憶體內建自我測試(MBIST)EDA工具使用,其元素化架構有助於構建高性價比的電路,還能與現有的MBIST電路共存,能插在需要上電測試的關鍵記憶體旁。SRAM_s代表原始SRAM介面,而SRAM_t代表MBIST處理後與SRAM的介面。透過多工器切換SRAM的控制訊號來保留原始架構,再以IP形式新增電路,產生SRAM_t介面。最後通過IEEE1500或IEEE1149.1介面接到頂層。其中,電路的插入需遵循各自的時鐘域(Clock Domain),當Clock Domain插入EZ-TEC後設定測試元件,即可連接到專用SRAM。

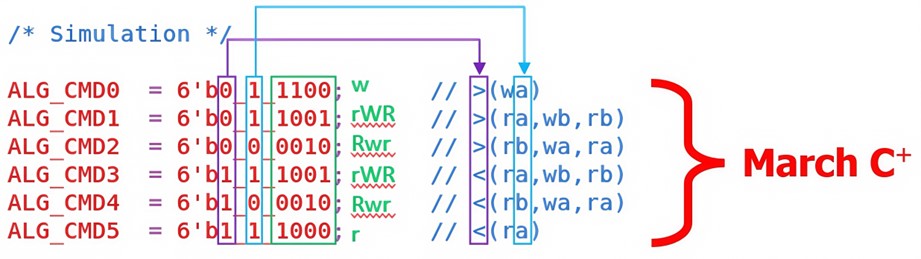

透過Element快速產生March C+演算法

EZ-TEC是基於芯測科技的美國專利「METHOD FOR GENERATING A MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT」的元素化架構。EZ-TEC能在CP測試階段,讓使用者根據使用需求來調整測試演算法的元素順序,如下圖W, rWR, Rwr元素。而使用者只需要準備四個元素,即可組成常見的March C+演算法。

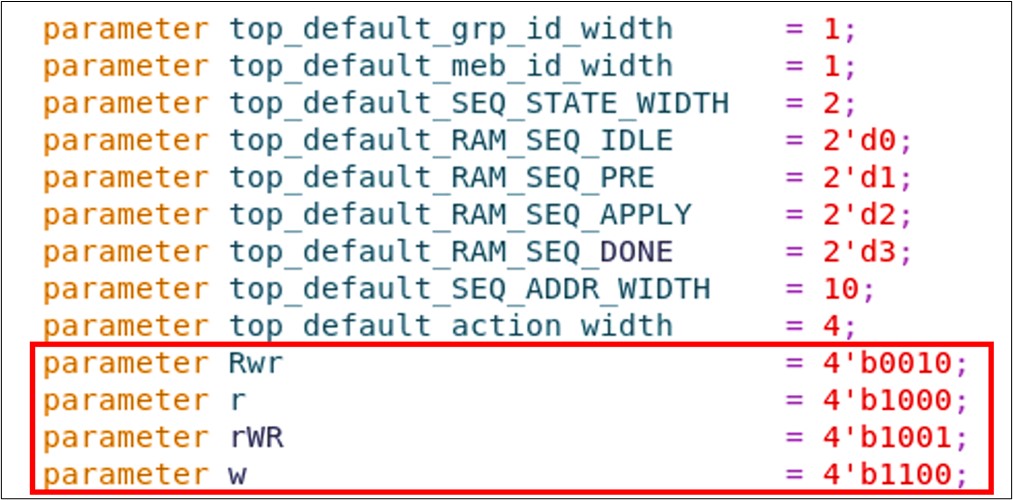

元素與代碼的組成

每個元件都有其相對應的代碼,使用者可以透過代碼的組合,排列出新的測試演算法。

改變測試演算法行為

使用者可以透過外部的Interface,如JTAG、Testbench中的send_command進行設定與更改測試演算法的行為。

send_command task

send_command = {PRL_ON, GRP_EN, MEB_ID, BG, ALG_CMD, MEN}

- PRL_ON:決定要並行測試

- GRP_EN:決定要測試的Group (每個代表1個Group)

- MEB_ID:決定要測試的Memory ID (「0」代表全部都測)

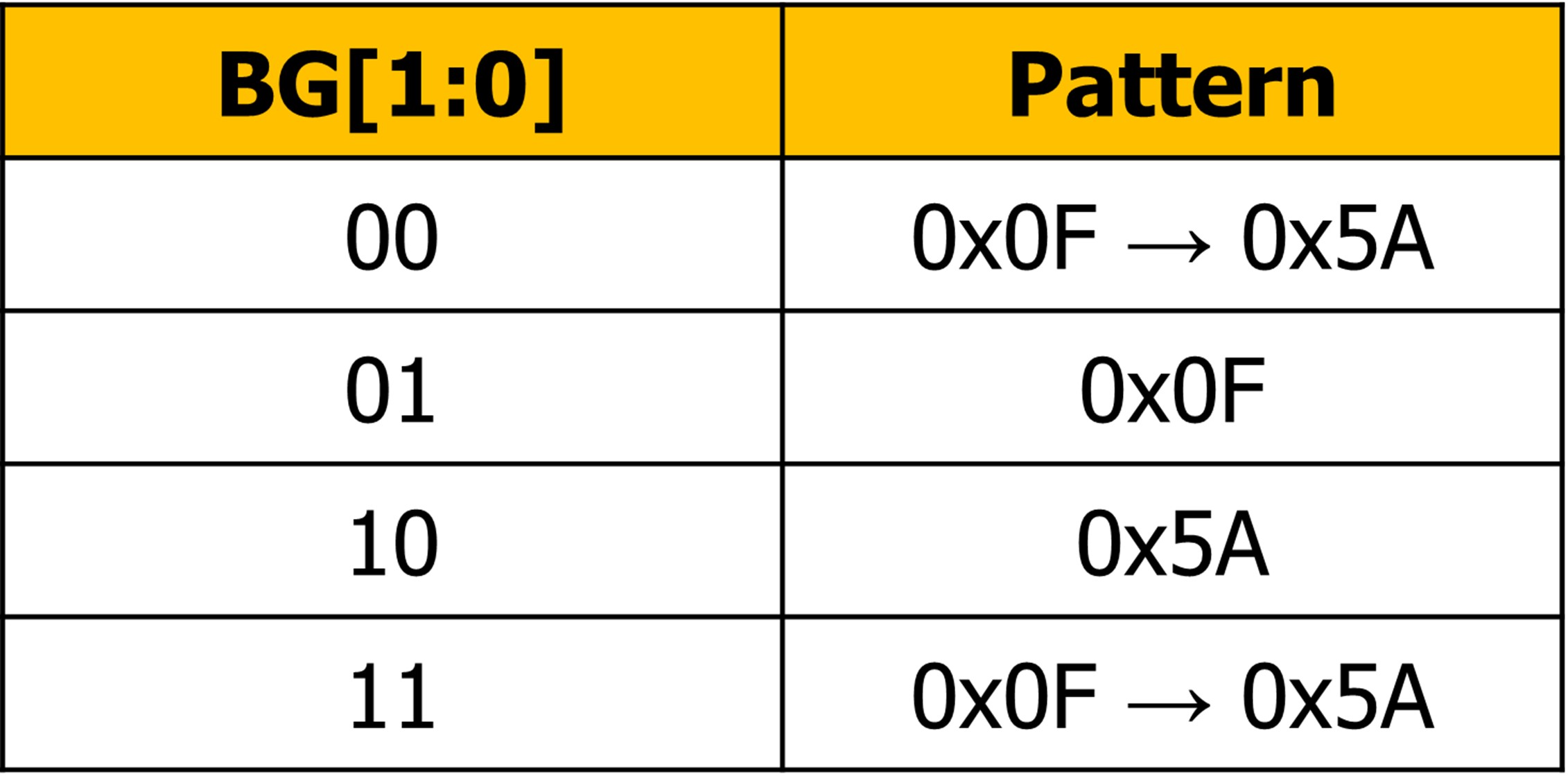

- BG:決定測試的Background順序

- ALG_CMD = {ALG_CMD12, ALG_CMD11, … , ALG_CMD1, ALG_CMD0}

- MEN:啟動Memory BIST測試

ALG_CMD

- ALG_CMD0~12 = {direction, cmd_parity, action}

- direction:address測試的順序 (0:升冪,1:降冪)

- cmd_parity:每個element的第一個讀/寫的background (1:a,0:b)

- action:由MBIST的code中,查出每個element代表的數值。

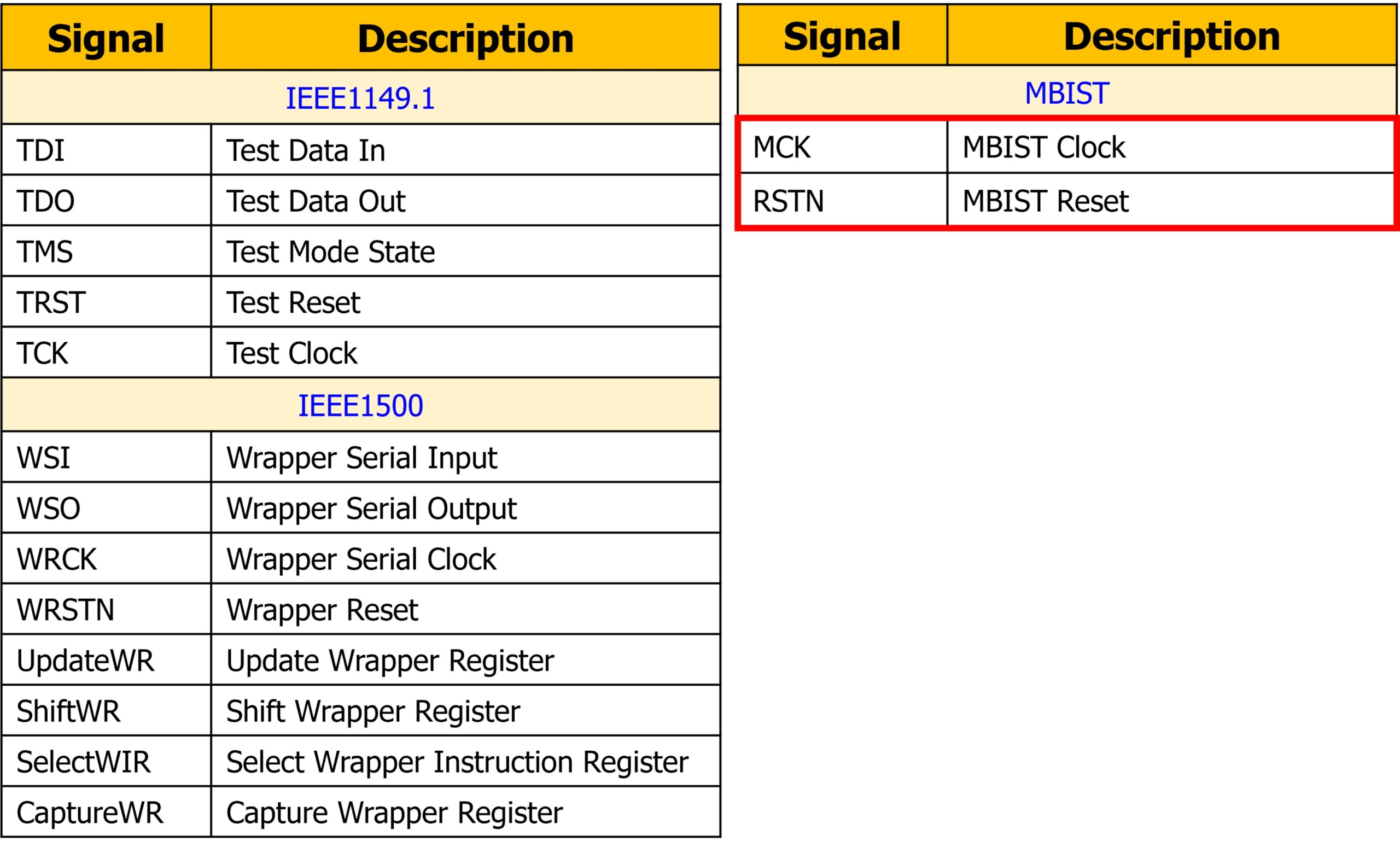

EZ-TEC介面腳位

EZ-TEC支援IEEE1149.1和IEEE1500介面。其中,MCK (Memory BIST Clock)為MBIST的時鐘訊號;RSTN (Memory BIST Reset)為MBIST的重置訊號。

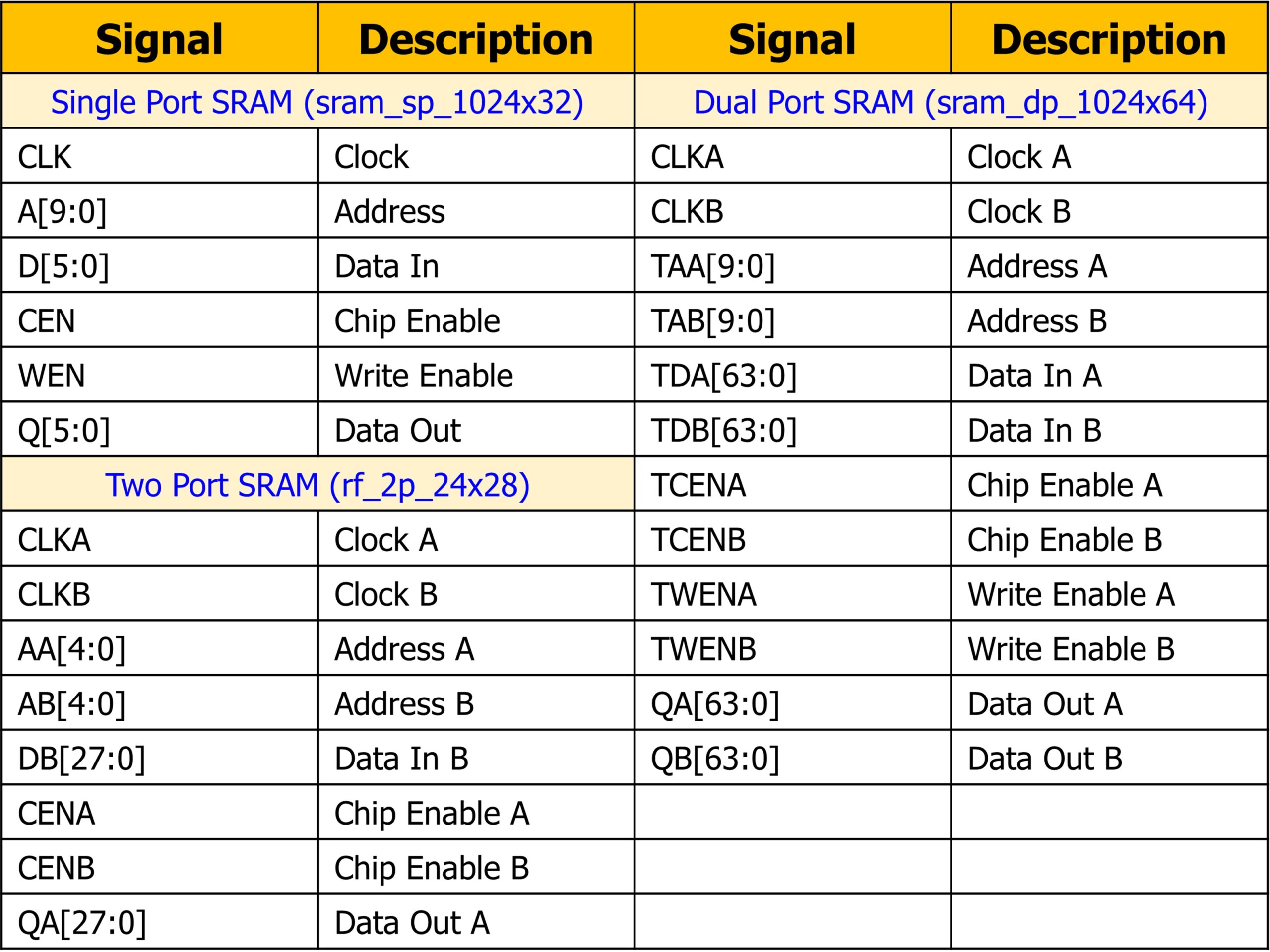

不同SRAM類型對應的介面

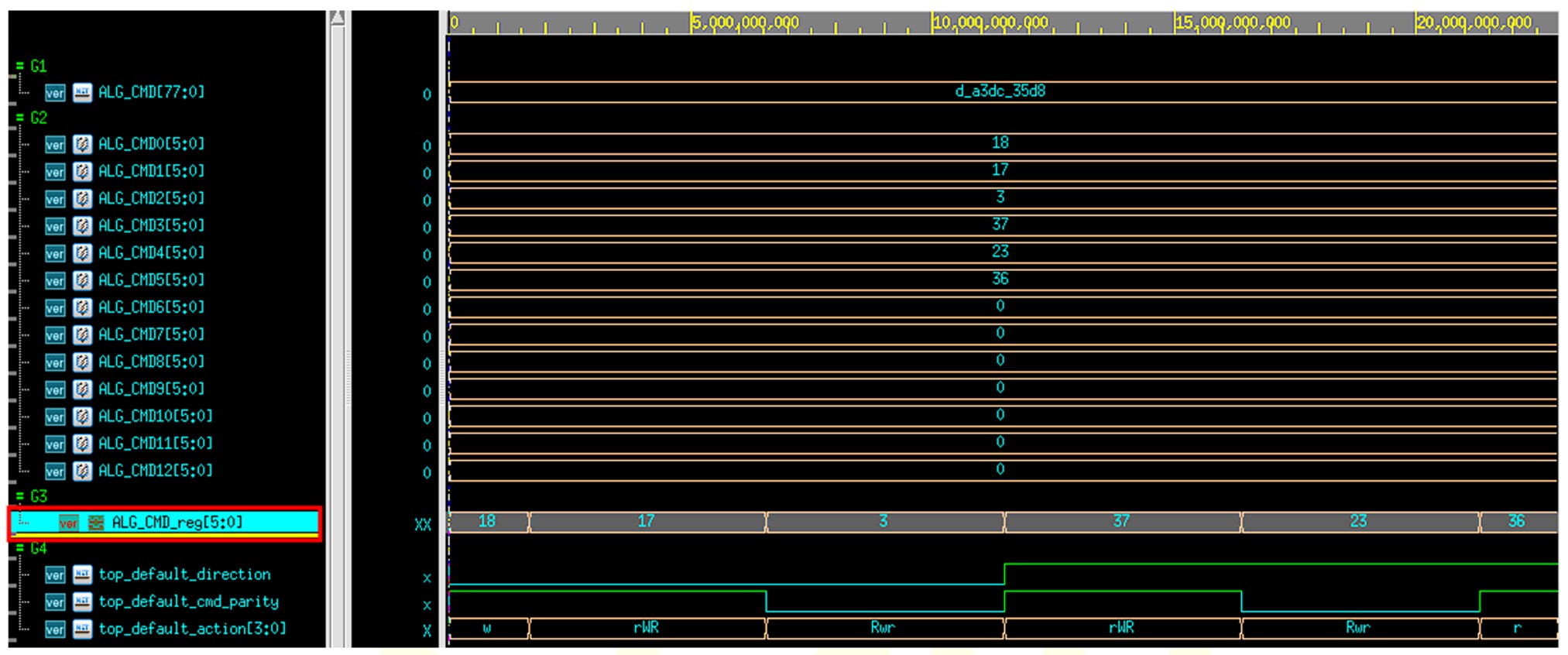

EZ-TEC波形圖

ALG_CMD集合0~12的訊號。每次位移6位元後存入ALG_CMD_reg,再依序執行March C+的演算法行為。

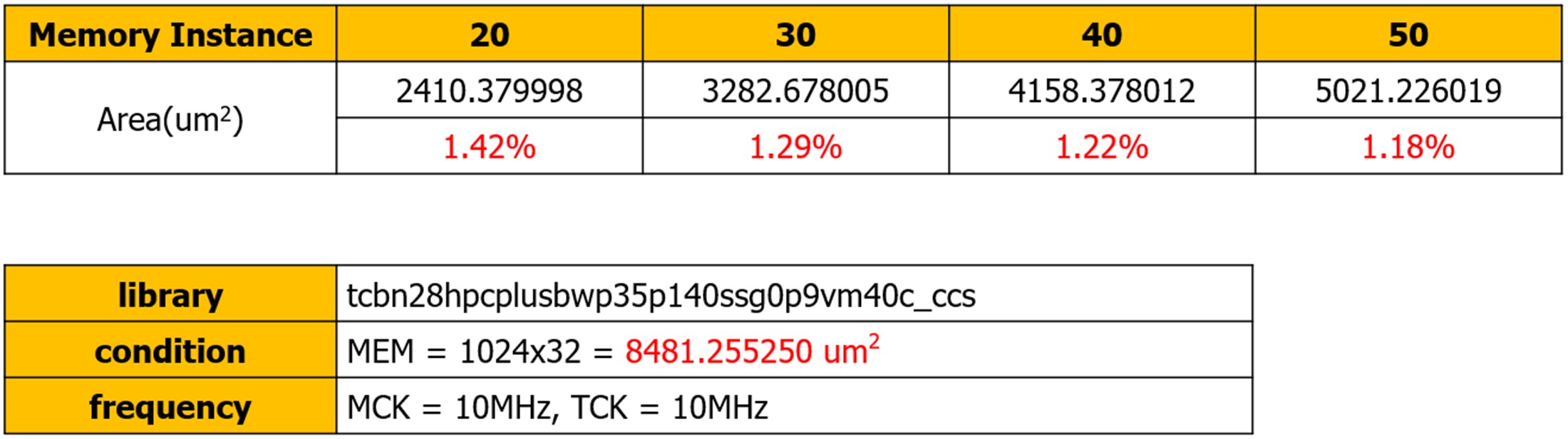

EZ-TEC面積占比

在面積的部分,芯測科技這邊採用了Hardware Sharing的概念,所以當SRAM的顆數越多,面積成長的比例就會越小。

晶片生產後,使用者可以透過EZ-TEC IP在CP測試階段時,調整演算法行為。無論是在不改變原始MBIST架構的情況下,或是採用其他廠商的MBIST方案,芯測科技的EZ-TEC IP都能針對重要或面積較大的SRAM重組排列出新的測試演算法,進而提高晶片的良率並降低DPPM。

2024技術文章