記憶體的使用至今已有近50多年的歷史,過去半導體的發展和應用不像現在如此先進及多元。從過去的PC與NB產品到手機、挖礦機的應用,再到2024年熱門的電動車及AI的風起雲湧,推動半導體邁向新的應用。

AI應用需要執行強大的運算功能,大幅提升SoC (系統單晶片) 內的記憶體占比。而傳統的March C演算法,已無法滿足各家晶圓業者對產品良率的要求。如果使用演算法無法有效的找出記憶體的瑕疵,就無法進一步使用修復的技術將晶片恢復到可以使用的狀態。為了滿足客戶對記憶體高強度及彈性化的測試需求,進而控制DPPM (Defective Parts Per Million,每百萬個產品所發生的不良品數量),芯測科技所開發的UDA和EZ-TEC IP能為客戶提供最佳的記憶體測試解決方案。

UDA (User-Defined Algorithm)

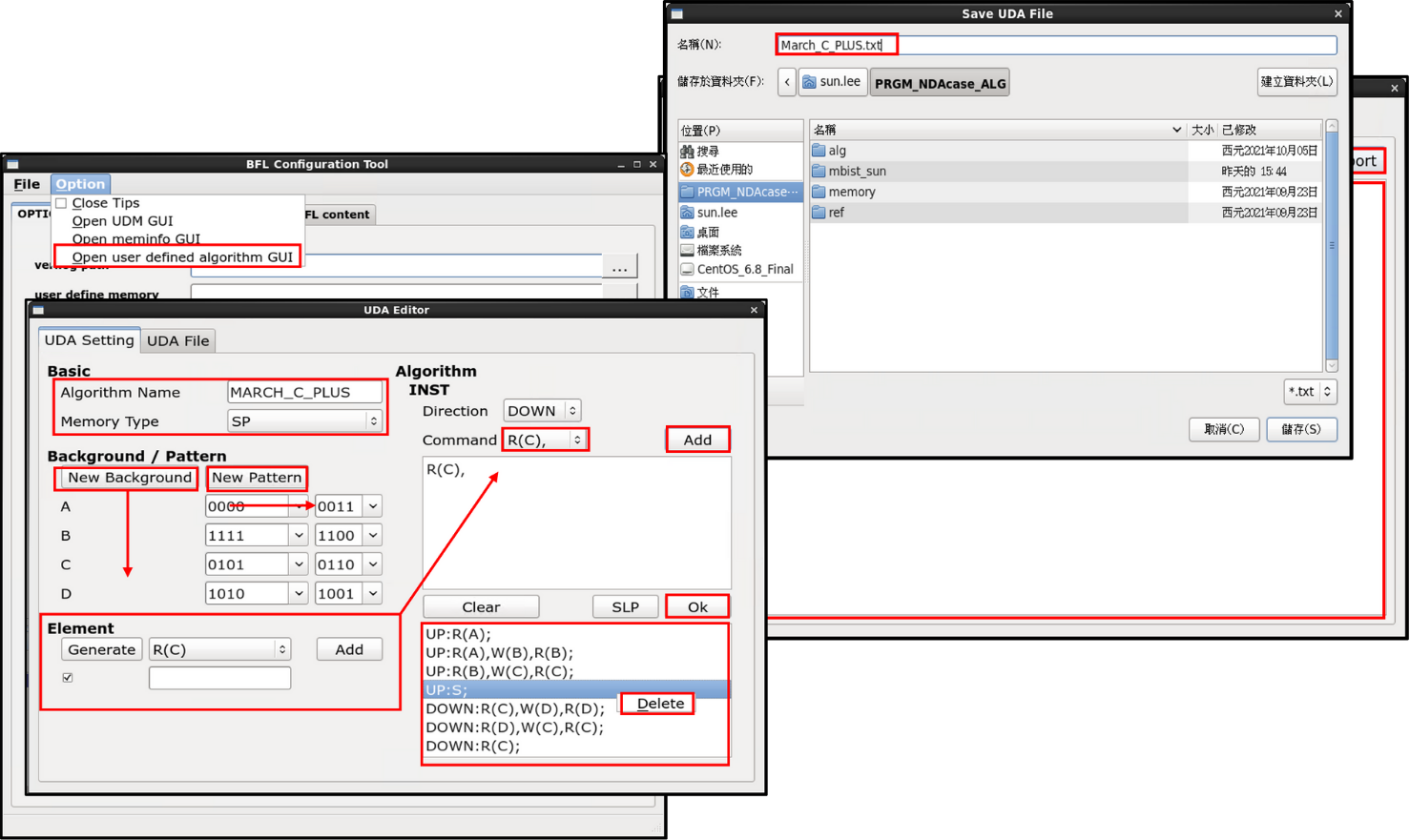

UDA (User-Defined Algorithm,使用者自定義演算法開發平台) 能滿足客戶對記憶體測試演算法的彈性化和自定義需求 。 晶片設計工程師也可以透過GUI (Graphical User Interface,圖形化操作介面) 快速產生記憶體測試演算法。CIM (Computing in Memory,記憶體內運算) 需要在記憶體上直接運算出結果,而不是透過CPU來運算。既有的測試演算法輸入及輸出的Pattern相同,意味著寫入的資料與讀取的資料相同,藉此比對記憶體的資料是否正確。因此針對CIM的記憶體,就需要能夠產生及比對出輸入資料與輸出資料是不同的Pattern,來驗證CIM記憶體是否正常。

UDA採用GUI介面

UDA採用GUI介面

EZ-TEC SRAM BIST IP

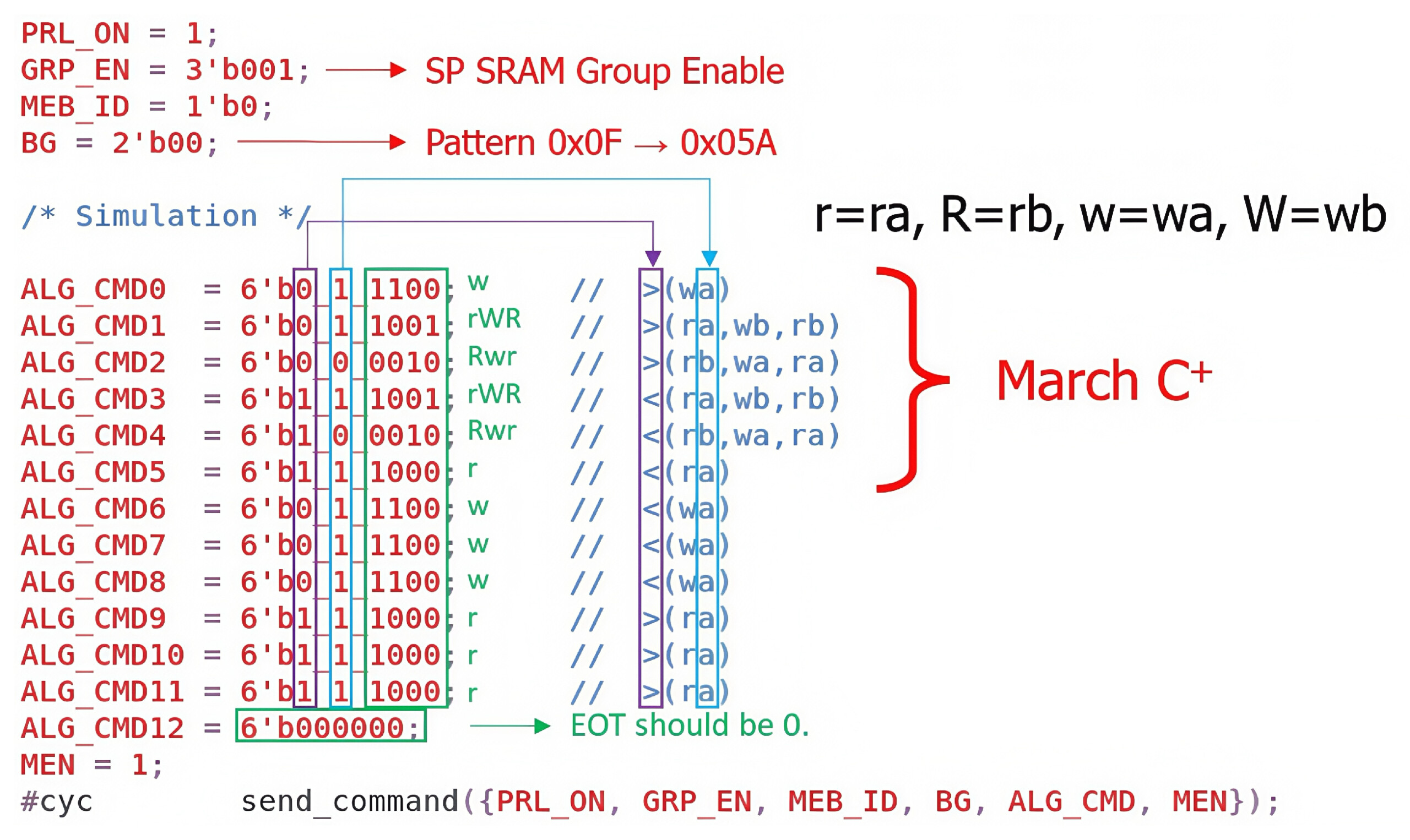

芯測科技的EZ-TEC是採用「用於產生記憶體自我測試演算法電路之方法 (METHOD FOR GENERATING AN MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT)」元素化架構的SRAM BIST IP。目前市面上常見的測試演算法,會有重複測試的行為,因此需要花費更多測試時間與成本。同時,先進製程不斷進度,現有的測試演算法可能無法偵測到先進製程的記憶體缺陷,也無法滿足與時俱進的需求。

芯測科技的EZ-TEC IP即是有效改善此現況的先進技術。同時提供測試工程師彈性的重組測試演算法。既有的測試演算法其執行順序在晶片設計完成就已固定,因此,進入晶片量產測試階段時,無法再做動態調整。EZ-TEC IP能夠在晶片量產測試階段,讓測試工程師能夠根據需求調整測試演算法的Element測試順序。另外也可以增加或減少元素執行的次數,進而提供記憶體測試的強度,將其不良的晶圓產品剔除,避免品質不佳的晶圓流到客戶端。

量產後利用元素調整測試演算法

量產後利用元素調整測試演算法

UDA搭配EZ-TEC可以合為一個獨立的IP,既不影響到客戶內部本身的DFT (Design for Testability,可測試性設計) 方案,還能加上芯測科技的解決方案,僅增加客戶微幅的成本,卻能達到顯著的晶片測試品質提升。如果搭配芯測科技的Repair修復技術,還能提高晶片的整體良率,降低DPPM,讓晶片達到最佳品質。

2024芯測小學堂