**iST/RT**

**July 2025**

# iSTART iReport 芯測科技電子報第 12 期

## 芯測科技榮獲「2025年度優秀車規芯片提供商」 殊榮,彰顯在車用電子領域的卓越實力

2025年6月19日 — 芯測科技於上海舉辦的「2025智能汽車芯片產業大會」中,榮 獲「2025年度優秀車規芯片提供商」獎項。本次大會由上海匠歆商務諮詢有限公 司、上海汽車芯片工程中心有限公司、上海智能感測器產業園、嘉定區集成電路 產業鏈聯盟聯合主辦,匯聚眾多車規芯片領域的領軍企業與技術專家。

此次獲獎充分肯定了芯測科技在車規電子領域的技術優勢。作為專注於EDA工具與IP解決方案的創新企業,芯測科技率先通過ISO 26262 TCL1 一級工具置信度認證,為車用晶片開發提供符合最高功能安全等級 ASIL D 的支援,助力客戶達成功能安全目標。

芯測科技的產品包涵UDA (使用者自定義測試演算法)、TEC (Test Element Chang)、Repair及POT (上電自我檢測)等功能,可大幅提升車用晶片的可靠性與測試效率。在車規晶片開發方面,其 eFlash 測試與修復方案尤為亮眼,成功協助多家客戶顯著縮短開發週期、提升晶片品質,並有效降低測試成本。

芯測科技對此次榮獲業界肯定深感榮幸。這不僅是對我們技術實力的高度認可, 更是對團隊持續創新精神的最佳肯定。展望未來,我們將持續精進投入車用電子 技術研發,並強化產品功能,攜手客戶共迎智慧汽車產業的嶄新未來。

## 「芯」疫苗問世!芯測自主研發UDA 打造SRAM全覆蓋測試方案

美國政府進一步擴大對中國地區半導體技術和EDA工具的出口限制,使得全球晶片設計產業面臨的供應風險日趨嚴峻。因應此波地緣政治帶來的不確定性,芯測科技強調,其關鍵測試演算法平台 UDA (User-Defined Algorithm) 完全由公司團隊自主開發,不依賴境外核心技術,可確保授權穩定性,為晶片設計業者提供穩定、安全的技術支援。

隨著半導體製程邁入FinFET、GAA等先進節點,SRAM的缺陷型態也如同病毒不斷變異,出現Marginal Fault、Dynamic Fault、Soft Error等新型態問題。傳統如March C這類標準測試演算法,猶如舊款疫苗,對於新型缺陷的防護力已漸顯不足。因應此艱鉅挑戰,芯測科技自主研發的使用者自定義演算法平台UDA (User-Defined Algorithm),就像一座靈活調配疫苗配方的研發基地,讓使用者根據產品特性與應用場景,自行組合最合適的測試策略,實現缺陷「全面接種」的防禦效果,確保SRAM在任何環境下都能穩定運作。

UDA平台採用圖形化操作介面與模組化設計,使用者無需編寫複雜程式碼,即可依據目標產品特性 (如高溫、低壓、低功耗)快速設計出客製化測試演算法。例如:針對高溫環境常見的Leakage Defect,可透過添加特定測試元素進行有效檢測,避免傳統演算法「遺漏感染」,導致產品後期失效。

芯測科技更進一步整合其獨有的TEC (Testing Elements Change)技術,使用者只需三個基本元素 (w, r, s),在CP與FT階段仍可靈活變化演算法的結構與深度,提升在有限測試時間內的檢測涵蓋率。與此同時,配合靜態與動態的背景控制策略,即可偵測包括SAF、TF、CF、WDF、DRDF等各類複雜缺陷。

iSTART iReport

3

此外,UDA平台亦可與芯測自家EDA工具如START™ v5與EZ-BIST整合使用,從 演算法設計到ATE Pattern產出形成一體化流程,全面提升測試自動化效率,降低 設計成本與驗證負擔。

面對AI、高效能運算、邊緣運算與車用電子等領域對記憶體品質日益嚴格的要求,芯測的UDA平台能快速針對特定缺陷生成最適化測試程序,宛如因應變異病毒的即時疫苗接種計畫,不僅提升良率,更能降低後端維修與保固風險,確保晶片在AI、車用、航太等關鍵領域的穩定運作。

| 特性           | 疫苗原理                                               | SRAM 測試演算法                                                                                          |

|--------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 設計目的         | 針對人體可能感染的病毒<br>或細菌所設計,透過模擬<br>或弱化病原體來「訓練」<br>免疫系統。 | 針對記憶體中可能發生的缺陷所設計,透過模擬各<br>種操作來「挑戰」記憶體,找出潛在錯誤。                                                       |

| 預防時機         | 能在真正的疾病發生前,<br>預先建立抵抗力,避免災<br>難性後果。                | 能在 IC 進入市場前,預先找出潛藏的缺陷,避免量<br>產後出現可靠度與功能問題。                                                          |

| 變化與挑戰        | 病毒不斷變異。                                            | 製程多樣化(例如 FinFET、GAA 等先進製程推進)使<br>得SRAM 缺陷也出現新型態 (如 Marginal Fault,<br>Dynamic Fault, Soft Error)。   |

| 應對方針         | 針對不同病毒(如<br>COVID、HPV、流感等)<br>打造不同疫苗。              | 根據目標產品特性 (高溫、高壓、低功耗等) 組合最合適的測試操作,打造客製化測試演算法。例如:高溫環境下易產生 Leakage Defect,就需針對這類Defect 加入特定測試 Pattern。 |

| 全面防堵<br>災難產生 | 全民接種疫苗。                                            | 全覆蓋設計的測試策略,可確保無論在何種使用情<br>境下 (溫度、電壓、頻率) ,SRAM 皆能正常運作。                                               |

## 芯測科技進行CIM研發 瞄準量子時代的資安市場

芯測科技致力於提供各類記憶體之測試與修復專用的EDA工具與IP,並針對授權客戶,提供涵蓋後端流程的一站式設計服務。

近年來,芯測科技積極投入Computing-In-Memory (CIM)架構的研發,重新定義AI運算的能效極限。

我們正在開發的SRAM-based CIM架構具備8-bit運算精度與極低功耗,並具延展性,可進一步支援RRAM架構設計,滿足不同應用場景的需求。

面對量子時代的資安挑戰,芯測科技亦率先導入格點密碼與NTT運算優化技術,透過CIM架構加速後量子密碼演算法,為智慧裝置與車用系統提供長效且穩固的安全保障。

芯測科技,除了進行SRAM-based CIM的開發,同時也提供CIM的測試電路開發環境,以創新的記憶體運算技術,驅動 AI 演算法更快、更強、更節能。

# 芯測科技成功通過 ISO/IEC 27001:2022 資訊安全管理系統認證

芯測科技專注於記憶體測試與修復解決方案的EDA工具、IP領域與雲端服務平台 iSTART-Cloud,獨家供應記憶體測試與修復解決方案,提供ASIC設計服務及雲端 EDA工具服務平台iSTART-Cloud,近期,芯測科技成功通過「國際認證機構-法 國標準協會AFNOR」之ISO/IEC 27001:2022資訊安全管理系統驗證。

芯測科技的雲端EDA工具服務平台對資訊安全管理有極高的要求,在會員網站安全防護上,除了透過密碼登入,還需搭配APP進行使用者的生物識別驗證,建立會員網站的安全性。此外,透過VPN連線設定,從瀏覽器連結至雲端桌面環境,可確保資料不受網路攻擊或竊取。在檔案上傳及下載的部分,使用者將檔案上傳到雲端後,當MBIST電路完成時,即可輕鬆地將檔案下載至本地機器中。不僅省下安裝及設定環境變數的步驟,還能讓使用不再受限。

ISO/IEC 27001:2022為世界公認的資訊安全管理標準,涵蓋風險評估、存取控制、數據保護及持續優化等關鍵領域。芯測科技透過系統化導入該標準,全面強化資訊安全政策與管理方針,確保客戶資料及企業營運資訊的機密性、完整性與可用性,有效保護客戶的資料安全與隱私權。

此次通過ISO/IEC 27001:2022資訊安全管理系統驗證,不僅是對芯測科技在資訊安全管理能力上的肯定,更代表芯測科技能滿足客戶、合作夥伴和法規機構對資訊安全的要求,確保各項資訊安全管理制度能貫徹執行與監管,使各項數位資產免於因外在威脅或內部不當管理遭受遺失、破壞或洩密等風險。

# 利用START™ v5完成Redundancy 和Stand-alone並存的SRAM修復技術

隨著製程的演進,人工智慧的蓬勃發展,記憶體的需求量逐漸升高,在此情況下,帶有修復功能的記憶體越發重要,但是如果一開始所使用的記憶體沒有自帶redundancy區塊,便無法進行修復,發生錯誤時只能將其拋棄,為此START™v5提供了相對應的解決方式,透過Stand-Alone的功能,產生redundancy區塊,讓原先無法修復的記憶體,透過這個區塊進行修復,並且可以依照使用者,設計redundancy區塊的大小,來符合使用者的需求。

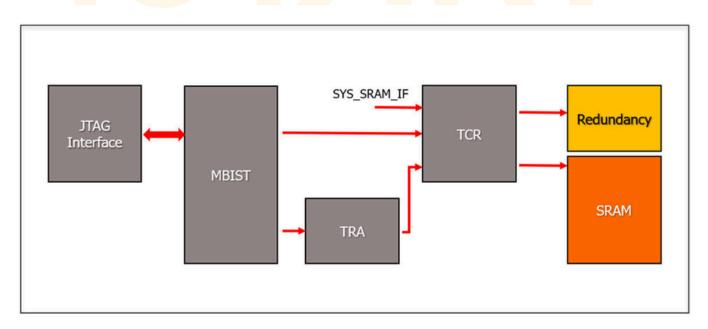

#### Stand-Alone Repair架構圖

架構如圖一,與之前的MBIST一樣,主要在於此功能會新增redundancy區塊,這區塊主要用來替換SRAM錯誤的地址,透過MBIST值錯SRAM,將錯誤資訊存至TRA中,透過TCR進行切換,TCR會負責將系統與BIST進行切換,以此來保證在系統執行的情況下,操作到錯誤的地址時,也能夠進行修復。

圖一、Stand-Alone Repair架構圖

#### 工具設定方式

Stand-Alone需要先填寫rmt (redundancy mapping file)檔,裡面會描述要做 Stand-Alone的memory hierarchy以及memory的repair資訊,檔案範例如圖二,若再redundancy memory hierarchy設定為istart的話,工具會產生對應 memory的redundancy module,方便使用者不用額外編寫redundancy的電路。

```

# hierarchy mapping format

# redundancy memory hierarchy(xx.x) = repair memory hierarchy(xx.x)

# ex. top.u_repair1_redundancy = top.u_repair1_ram

istart = top.sp_rpram

# repair memory format

# [memory module name] : redundancy_type = row, redundancy_count = 2(num)

# ex. [SL180_8192X8X4CM32] : redundancy_type = row, redundancy_count = 2

[SL180_8192X8X4CM32] : redundancy_type = row, redundancy_count = 2

```

圖二、rmt (redundancy mapping file)檔範例

編寫完rmt檔案後,需要在BFL的設定檔中,設定圖三的選項。

```

set redundancy_mapping = ./redundancy_mapping.rmt

```

圖三、BFL 撰項

#### 模擬方式

工具會產生相對應的fault module,因為在模擬fault時,會同時存在一般memory以及本身帶有redundancy的memory,所以在模擬時需要define REPAIR,確保我們工具產生的fault module只作用在Stand-Alone memory上。

```

`ifdef FAULT

`ifdef REPAIR

SRAM

`else

SRAM_f

`endif

`else

SRAM

`endif

```

```

`ifdef FAULT

Stand_Alone_SRAM_f

`else

Stand_Alone_SRAM

`endif

```

圖四、Fault module define

流程分為BFL以及BII,在相對應的流程都會產生模擬的環境,BFL階段模擬指令及結果如圖五、圖六,BII階段模擬指令及結果如圖七、圖八。

make controller\_name FUNC=tb\_INS\_RP\_f

圖五、BFL模擬指令

Test Result: Failed!

Repairing and Re-testing

Test Result After Repair: Pass!

圖六、BFL模擬結果

make integ\_name FUNC=tb\_f

圖七、BII模擬指令

圖八、BII模擬結果 (Soft repair)

## 車規級別晶片的SRAM測試算法三部曲之 漫談車用電子晶片的DPPM

DPPM (Defective Parts Per Million,每百萬顆中的不良品數)是衡量車用晶片品質與可靠度的核心指標。當一顆晶片出現在煞車系統或自動駕駛控制單元中時,即使僅有百萬分之一的故障機率,也可能釀成無法挽回的事故。因此,從設計、製程、測試到驗證,每個環節都要以極低的 DPPM 為目標。

本集將介紹不同晶片類型 (如 Power IC、MCU、雷達感測 IC)在量產與保固期內的DPPM目標、Tier 1與OEM對品質的實際要求,以及 AEC-Q100、IATF 16949、ISO 26262等國際標準如何影響業界的DPPM管理策略。透過完整的背景脈絡與數據整理,幫助觀眾理解車用晶片品質控管的嚴謹程度與實務做法。

#### 重點速覽

- DPPM的背景與指標期望

- 市場召回的DPPM期望

- 國際標準與規範參考

- 不同晶片類型的DPPM指標

- DPPM管理的背景脈絡

#### <u>▶ 觀看完整影片</u>

# 車規級別晶片的SRAM測試算法三部曲之 車用晶片面臨的SRAM失效種類

在汽車應用中,SRAM扮演著暫存與高速緩衝的重要角色,但它也暴露在極端溫度 與電壓環境下,容易出現各種潛在失效。對於需達到ISO 26262 ASIL-C或ASIL-D 的車用晶片來說,任何一種記憶體缺陷都可能導致系統功能安全風險。因此,我 們必須了解並覆蓋所有潛在的SRAM失效類型。常見的失效大致可依操作行為分為 三類:

#### 寫入操作

- 固定型故障 (Stuck-At Fault, SAF):儲存單元無法被寫成0或1,通常是由於上拉電阻或下拉電阻的電晶體損壞。

- 寫入干擾錯誤 (Write Disturb Fault, WDF): 對某個cell寫入時,鄰近的cell意外被翻轉。

- 存取故障與開路故障 (Acc<mark>es</mark>s Fau<mark>lt, Open Fault)</mark>:如wordline或bitline導通 異常,導致訊號無法正確寫入。

#### 讀取操作

- 固定型故障:與寫入類似,但這裡是感測電路錯誤,導致讀取值一直是錯誤狀態。

- 讀取干擾錯誤 (Read Disturb Fault, RDF): 讀取動作意外改變cell內資料,特別是資料保留力弱的cell。

- 偽讀破壞故障 (Deceptive Read Destructive Fault, DRDF):表面讀取成功,

但實際已悄悄破壞cell內的資料。

- 資料保持錯誤 (Data Retention Fault, DRF): 在特定時間後資料自動消失,

常與漏電或閂鎖效應較弱有關。

#### 寫入加讀取的組合操作

- 轉換錯誤 (Transition Fault, TF): cell無法從0切換到1,或1切換到0,需透過交替寫入與讀取來偵測。

- 動態錯誤 (Dynamic Fault):例如兩次寫入與兩次讀取的操作中才會出錯,需仰賴如March C-、March SS等測試演算法來捕捉。

針對車用SoC的環境與可靠度要求,以上這些失效類型都是高風險,必須一一覆蓋。例如WDF、RDF、TF與DRF在高溫、高壓或低溫、低壓下都會更加嚴重,特別需要透過客製化測試演算法來針對性覆蓋。

芯測科技設計一套專門針對這些失效類型的SRAM測試算法。利用UDA (使用者自定演算法)與TEC (Test Element Change)技術,可以靈活產生具備高覆蓋率的測試序列,不但能強化車用晶片品質,也能達成ASIL-C/D等級的功能安全要求。

▶ 觀看完整影片

## SRAM測試演算法中的讀寫操作與缺陷類型

- 寫入操作主要可以偵測出固定型故障、寫入干擾錯誤、存取故障,以及開路故障。

- 讀取操作則能偵測出感測階段的固定型故障、讀取干擾錯誤、偽讀破壞故障, 以及保存故障。

- 結合寫入和讀取的序列則可以偵測出轉換故障、動態故障,以及邊界穩定性問題。

為了執行上述特定的讀取和寫入操作,並有效偵測各種缺陷,iSTART-TEK的TEC和UDA功能提供了強大的支援。

UDA是一個可配置的SRAM測試平台,能夠讓使用者依需求設計特定的讀寫操作序列,並且支援各類March測試。

TEC則提供了更高的靈活性,即使在CP階段後,仍可透過樂高堆疊式的模組化測 試元素,調整或微調測試演算法。

這兩項技術結合在一起,使我們能夠有效地偵測因電壓與溫度變化而產生的各種 SRAM缺陷。

▶ 觀看完整影片

### 如何改寫測試演算法的架構?

科技發展日新月異,傳統的演算法在晶片下線後無法修改演算法行為,導致有些晶片雖然通過了CP測試 (Chip Probe Test,裸晶測試)和FT測試 (Final Test,最終測試),但在使用過程中仍有可能出現缺陷的問題。若在此時新增測試演算法,將會增加不少的測試時間和成本。因此,演算法的彈性化與複雜度成為一門重要的課題。

#### **Testing Elements Change (TEC)**

芯測科技所開發的 TEC (Test Element Change) 以 GUI (圖形化操作介面)將演算法的行為元素化,藉由元素的重新排列,組合成新型態的演算法。即使客戶未採用芯測科技的 MBIST 電路,也可以保留原始的 BIST 架構,並以 EZ-TEC SRAM BIST IP 的形式插入原始電路,為客戶的整體應用帶來極大的便利性和彈性。當使用者發現 SRAM 有問題卻無法以原始 MBIST 電路偵測出 Defect,在不修改 SRAM 架構的前提下,使用者可以透過 EZ-TEC SRAM BIST IP 增加新的測試演算法來解決 Defect 問題,有效提高良率。

EZ-TEC SRAM BIST IP 是基於芯測科技美國專利「METHOD FOR GENERATING AN MEMORY BUILT-IN SELF-TEST ALGORITHM CIRCUIT」的元素化架構,每個元素都有相對應代碼,透過代碼即可產生新的演算法。使用者只需準備『四』個元素,就可以組合成常見的 March C+ 演算法,如下圖。

```

PRL ON = 1;

GRP EN = 3'b001; → SP SRAM Group Enable

MEB ID = 1'b0;

→ Pattern 0x0F → 0x05A

BG = 2'b00; -

r=ra, R=rb, w=wa, W=wb

/* Simulation */

ALG CMD0 = 6'b0 1 1100

>(wa)

11

ALG\_CMD1 = 6'b|0||1||1001|; rWR

>(ra,wb,rb)

>(rb,wa,ra)

<(ra,wb,rb)

11

March C<sup>+</sup>

ALG CMD3 = 6'b1 1 1 1001; rWR

11

ALG CMD4 = 6'b|1||0||0010| Rwr

<(rb, wa, ra)

//

ALG CMD5 = 6'b|1|1|1000;

//

< (ra)

ALG CMD6 = 6'b0 1 1100; w

11

<(wa)

<(wa)

ALG CMD7 = 6'b|0||1||1100| w

11

ALG_CMD8 = 6'b0 1 1100; w

ALG_CMD9 = 6'b1 1 1000; r

>( ra)

//

ALG CMD10 = 6'b1 1 1000; r

|>|( r|a|)

ALG CMD11 = 6'b|1|1|1000; r

>( ra)

ALG CMD12 = 6'b000000:

EOT should be 0.

MEN = 1;

send command({PRL ON, GRP EN, MEB ID, BG, ALG CMD, MEN});

#cyc

```

#### 主要優勢

- 獨立運行於任何MBIST並與現有的記憶體測試電路並存。

- 原始MBIST電路無法檢測出特殊記憶體缺陷時,可透過元素重組重新測試。

- 透過Building-Block架構能構建出最具成本效益的電路。

- 針對重要的記憶體重組新的演算法來進行測試,確保記憶體測試的覆蓋率。

- 輕鬆選擇記憶體測試演算法元素,提高晶片設計的靈活性和可靠性。

- 有效降低DPPM與測試成本。

芯測科技的EZ-TEC SRAM BIST IP提供彈性重組測試演算法。能在CP/FT階段,讓測試工程師修改測試機台的Pattern,進而提高記憶體測試的強度,為使用者帶來極大的便利性與彈性。

#### <u>▶ 觀看完整影片</u>

## BIST與BISR對SoC的影響

#### BIST和BISR對SoC的影響

以近期熱門的話題ChatGPT為例,ChatGPT屬於AI應用,AI處理需要透過高端的CPU或GPU來做運算,而這些複雜的運算需要使用大量的記憶體,來確保記憶體的正常運作。SoC從晶圓製造廠出來後,需要透過BIST來做檢測,當檢測到記憶體有問題時,再用BISR來修復。此外,AI的晶圓需採用先進的製程來製造,製造過程中可能會發生靜態失效或動態失效的問題。

#### BIST和BISR使用方式

BIST自我檢測電路可精準地將靜態失效和動態失效檢測出來,但只能檢測出瑕疵的部分。若要將壞的晶圓變成可以使用的chip就需要透過修復方案BISR將壞的記憶體取代,並使用好的Redundancy記憶體讓晶圓恢復正常運作。

#### BIST和BISR主要優勢

芯測科技在BIST和BISR上擁有將近40項的專利,其中透過多樣化且高執行效率的 記憶體測試演算法所產生的BIST和BISR電路面積也是最小的。另外,透過客戶使 用反饋,證明芯測科技的EDA工具在各類型的晶片上,都能快速產生BIST和BISR 電路,協助客戶檢測出記憶體的缺陷,有效地提升客戶SoC的品質與良率。

#### <u>▶ 觀看完整影片</u>