### iST/RT The Diagnosis Tool for Memory Testing and Development of Automotive SoCs

Automatic test equipment (ATE) is commonly used for SoC testing. The ATE then generates a log file of the testing results. When the ATE log file only consists of the signals 0 or 1, this log file is not easy to understand without using analysis tools. To simplify and expedite the analysis of ATE testing results for memories, the ATE diagnosis tool of START<sup>™</sup> v3 is introduced. Along with the files generated by iSTART tools, it can easily analyze faulty memory information. iSTART has also developed a PC-based EZ-Debug, that can debug some chips after shuttle tape out or chips under development. This tool helps reduce ATE testing costs and obtain real-time diagnosis results.

### I. EZ-Debug

### 1. The Block Diagram of the EZ-Debug

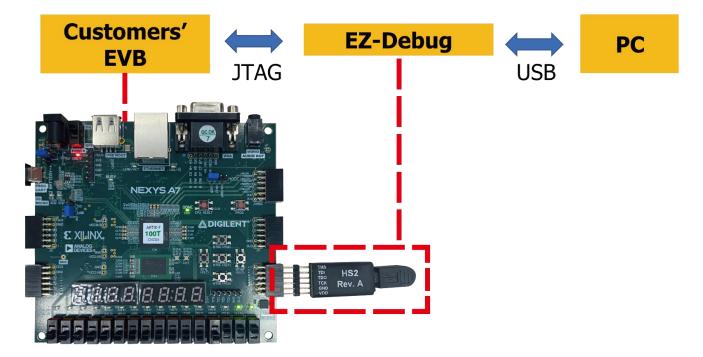

The EZ-Debug debugging tool makes diagnosis convenient by allowing communication between the PC and FPGA through an adapter cable. This tool is primarily used for simulating some chips after shuttle tape out or chips under development. The adapter cable and tool specifications are shown in the figure below. The PC connects to the adapter cable via USB, and the adapter cable and tool convert the signals to JTAG (IEEE 1149.1) for FPGA/IC diagnosis.

The figure below shows actual usage. The red box indicates the adapter cable, with the FPGA on the right side and the PC on the left side.

# iST/RT

2. Actual Applications:

Start by referring to the "bist\_testing" task in the complete INTEG testbench. In this task, we can find information about "CMD\_DATA" as shown in the figure below. Then, fill in the input binary value based on the information in the figure and use TDI of JTAG (ieee1149.1) to do send\_command to start testing.

| <pre>{top_default_DIAG, top_default_ALG,</pre>     |

|----------------------------------------------------|

| <pre>top_default_SEQ_ID, top_default_GRP_ID,</pre> |

| <pre>top_default_MEB_ID, top_default_MEN};</pre>   |

Signal Interpretation:

**Controller\_name\_DIAG:** It determines whether to execute the diagnosis or not. When set to 1, it will be activated.

**Controller\_name\_ALG:** When the program\_algorithm in the BFL option is enabled, the Controller\_name\_ALG command will be generated in the testbench to control the algorithm that is to be tested.

Controller\_name\_SEQ\_ID, Controller\_name\_GRP\_ID and Controller\_name\_MEB\_ID: These are used to specify the memory IDs that are to be tested.

Controller\_name\_MEN: It is the command that enables the Controller BIST. When set to 1, it will be activated.

The TDO of JTAG will generate capture\_commad. Users can interpret the content of capture\_commad by referring to the "test\_result" signal arrangement in the INTEG testbench shown in the figure below.

```

{top_default_MGO, top_default_MRD,

top_default_SRD, top_default_LATCH_GO} = top_default_test_result;

```

Signal Interpretation:

**Controller\_name\_MGO:** This is the BIST testing result. It will be 0 when the BIST testing fails. **Controller\_name\_MRD:** It will be 1 when the BIST testing is completed.

**Controller\_name\_SRD:** It will be 1 when diagnosis data is ready and can be captured.

**Controller\_name\_LATCH\_GO:** The width of this signal depends on the memory amount in the meminfo file generated by START<sup>™</sup>. When each signal in LATCH\_GO changes from 1 to 0, it means that the memory testing fails.

### **iST/RT**

#### II. ATE Diagnosis Tool

START<sup>™</sup> v3 (BFL & BII) Settings:

- 1. \*.bfl Settings

- A. diagnosis\_support and diagnosis\_width\_info Settings

- i. diagnosis\_support: START<sup>™</sup> v3 provides a diagnosis mode and reports diagnostic information.

- ii. diagnosis\_width\_info: Align the length of test information to facilitate diagnosis and interpretation.

- B. diagnosis\_faulty\_items: This provides users with the option to select diagnostic information for their own designs, including algorithms, algorithmic units, algorithmic elements, memory grouping locations, memory addresses, and memory data.

define{BIST}

| ine (D101)                            |              |            |          |                            |          |           |          |  |

|---------------------------------------|--------------|------------|----------|----------------------------|----------|-----------|----------|--|

| set diagnosis_support                 | = yes        | # yes, no  |          |                            |          |           |          |  |

| set diagnosis_width_info              | = yes        | # yes, no  |          |                            |          |           |          |  |

| <pre>set diagnosis_faulty_items</pre> | = algorithm, | operation, | element, | <pre>seq_id, grp_id,</pre> | address, | ram_data, | rom_data |  |

2. \*.bii Settings :

A. Under define{Testbench}[INTEG\_tb], choose the STIL as file\_format to generate a memory test pattern STIL file after simulation.

| det | fine{Testbench}[INTEG_tb] |   |      |   |                                    |

|-----|---------------------------|---|------|---|------------------------------------|

|     | set pll_wait_cycle        | = | 10   |   |                                    |

| 1.1 | set reset_cycle           | = | 10   |   | <pre># integer bigger than 0</pre> |

|     | set file_format           | = | STIL | # | verilog, STIL                      |

|     |                           |   |      |   |                                    |

Introduction of the Diagnosis Tool Interface:

|   |                                                                                                                                              | iSTART-DA | × |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|

| 1 | iSTART-Diagnostic_Analytics<br>Import STIL:<br>Import ATE Log:<br>Import Meminfo:<br>FAULT_BIT_WIDTH_INFO: 16 클<br>DIAGNOSIS WIDTH_INFO: 8 클 |           |   |

| 2 | Convert Run Export                                                                                                                           |           |   |

| 3 |                                                                                                                                              |           |   |

|   | 0%                                                                                                                                           |           |   |

| 4 | Ver. : 1.4.20220221                                                                                                                          |           |   |

1. Files and Settings:

4

- A. Import the STIL file for ATE: The STIL file will generate the corresponding memory test pattern based on the options set in START<sup>™</sup> v3 (as the START<sup>™</sup> v3 settings mentioned above).

- B. ATE log: It is the file of the ATE testing result.

- C. meminfo File: This is generated by START<sup>™</sup> and it contains all the information of the memories.

# if the instance is the alais type , The \*\* is .

[DOMAIN=top\_default, cycle=100.0ns]

[CTR] # Hier: top

[SEQ] # No.= 1,InstanceNo= 3,SEQ\_max\_addr\_size= 1024,Hier: top u\_t1

[GROUP] # No.=1\_1

[SP=1\_1\_1, byp=no, diag=no, q\_pipe=no, repair=no] sram\_sp\_1024x32

[SP=1\_13, byp=no, diag=no, q\_pipe=no, repair=no] sram\_sp\_1024x32

[SEQ] # No.= 2,InstanceNo= 1,SEQ\_max\_addr\_size= 24,Hier: top u\_t1

[GROUP] # No.=2,I

[GROUP] # No.=2,I

[GROUP] # No.=2,I

[GROUP] # No.=2,I

[DP=3\_1\_1, byp=no, diag=no, q\_pipe=no, repair=no] rf\_2p\_24x28

[SEQ] # No.= 3,InstanceNo= 1,SEQ\_max\_addr\_size= 1024,Hier: top u\_t1

[GROUP] # No.=3,I

[DP=3\_1\_1, byp=no, diag=no, q\_pipe=no, repair=no] sram\_dp\_1024x64

###Total mbist memory instance = 5

###Total SRAM/REGFILE = 3

###Total SRAM/REGFILE = 4

##

#### Set FAULT\_BIT\_WIDTH and DAGNOSIS\_WIDTH.

# iST/RT

- Convert: Perform conversion after importing all files. Run: Perform analysis after conversion. Export: Export the analysis result as a txt file.

- 3. Tool Execution Information: This section provides information and status updates for the tool execution

- 4. Progress Bar and Version Number

- 5. Tool Analysis Results: The tool's analysis result will be generated in this section.

Analysis Method: After importing all files and settings, the tool first analyzes the ATE result file and locate the faulty patterns. It then cross-references the STIL file to find and analyze the corresponding test commands. After analysis, it compares the memory order in the meminfo file and prints out the problematic memory information when exporting the result.

Analysis Result: The tool analysis is shown in the figure below. The right-hand block displays detailed information about the faulty memory, including the controller, memory type, memory hierarchy, and the information set in diagnosis\_faulty\_items of START<sup>™</sup> v3.

Authored by Hank Chen, Senior Engineer at iSTART-TEK