# **EZ-BIST User Manual**

**v3.3**

## Contents

| 1. | Intro        | oduction to EZ-BIST                       | 1    |

|----|--------------|-------------------------------------------|------|

|    | 1.1.         | Features                                  | 1    |

|    | 1.2.         | , c c                                     |      |

| 2. | EZ-E         | BIST Command Options and Parameters       | 3    |

|    | 2.1.         | Invoke EZ-BIST with the GUI Mode          | 4    |

|    | 2.2.         | Input Verilog Files                       | 5    |

|    | 2.3.         | Specify the Working Path                  | 7    |

|    | 2.4.         | Auto-Identify the Memory Model            | 8    |

|    | 2.5.         | The Generate the ROM Signature            | 9    |

|    | 2.6.         | Template File Generator                   | 9    |

|    | 2.7.         | Input BFL File                            | . 10 |

|    | 2.8.         | Insert MBIST to Design                    | . 10 |

|    | 2.9.         | Specify Top Module                        |      |

|    |              | Disable Clock Tracing                     |      |

|    |              | Input UDM File                            |      |

|    |              | Generate UDM File in GUI Mode             |      |

|    |              | Integrate Multiple MBIST Circuits         |      |

|    |              | Generate UDM File with Library File       |      |

|    |              | Generate UDM File with Configuration File |      |

|    |              | Parsing Type Definition                   |      |

|    |              | Fault Free                                |      |

|    | _            | RCF Generator                             |      |

| _  |              | STIL Format                               |      |

| 3. |              | SIST BFL Options                          |      |

|    | 3.1.         |                                           |      |

| 4. | 3.2.         |                                           |      |

| 4. |              | BIST Output FilesSelf-MBIST Related Files |      |

|    | 4.1.<br>4.2. | Insert MBIST Related Files                |      |

|    | 4.2.<br>4.3. |                                           |      |

|    | 4.3.<br>4.4. |                                           |      |

|    |              | Macro File                                |      |

| 5. |              | ile                                       |      |

| J. | 5.1.         | Integrator Function Block                 |      |

|    | 5.1.<br>5.2. | Testbench Function Block                  |      |

| 6. |              | endixes                                   |      |

| ٠. |              | "Include" Case                            |      |

|    | J. I.        |                                           | . 00 |

### **EZ-BIST User Manual v3.3**

| 6.2. | Parsing Mode                 | 80 |

|------|------------------------------|----|

|      | *.rcf File                   |    |

| 6.4. | Supported Testing Algorithm  | 81 |

| 6.5. | Statistics in TSMC SP Memory | 84 |

## **List of Figures**

| Figure 1-1  | EZ-BIST Operation Flow Diagram                     | 2    |

|-------------|----------------------------------------------------|------|

| Figure 2-1  | EZ-BIST Command Options                            | 3    |

| Figure 2-2  | EZ-BIST GUI Mode                                   | 4    |

| Figure 2-3  | Verilog File Path                                  | 5    |

| Figure 2-4  | File-list File Example                             | 6    |

| Figure 2-5  | Work Path                                          | 7    |

| Figure 2-6  | Memchecker Information                             | 8    |

| Figure 2-7  | The Example of *_gold_signature.txt                | 9    |

| Figure 2-8  | EZ-BIST Template Generator                         | 9    |

| Figure 2-9  | Top Module Name                                    | 11   |

| Figure 2-10 | User Defined Memory                                | . 12 |

| Figure 2-11 | Open UDM GUI                                       | . 13 |

| Figure 2-12 | Support Batches Adding and Multiple Formats        | . 14 |

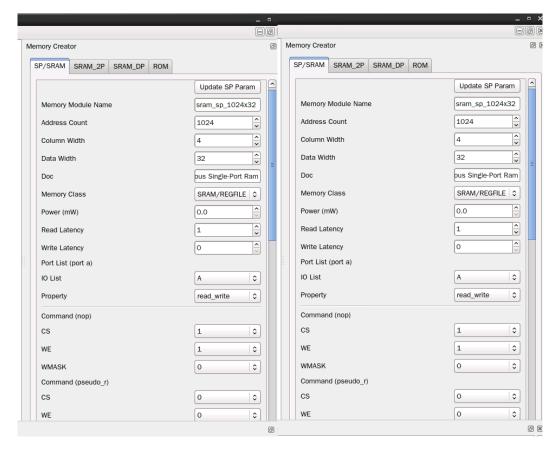

| Figure 2-13 | Memory Parameter Settings                          | . 15 |

| Figure 2-14 | IO Editing through EZ-BIST                         | . 16 |

| Figure 2-15 | IO Adding Rapidly Using Drag & Drop                | . 16 |

| Figure 2-16 | Delete IO with Right Click                         | . 17 |

| Figure 2-17 | User Define Memory Generation                      | . 17 |

| Figure 2-18 | UDM Configuration File Example                     | . 19 |

| Figure 3-1  | OPTION Function Block                              | . 22 |

| Figure 3-2  | Block Diagram of System Design with MBIST Inserted | . 24 |

| Figure 3-3  | Clock Sub Function Block                           | . 26 |

| Figure 3-4  | Group Function Block                               | . 28 |

| Figure 3-5  | Open Memory Info File                              | . 30 |

| Figure 3-6  | Example of Memory Info File                        | . 31 |

| Figure 3-7  | Support Batches Adding and Multiple Formats        | . 31 |

| Figure 3-8  | Memory Info Setting Information                    | . 32 |

| Figure 3-9  | PHYSICAL Sub Function Block                        | . 33 |

| Figure 3-10 | MBIST Function Block                               | . 35 |

| Figure 3-11 | Example of Synchronous/Asynchronous Circuit        | . 38 |

| Figure 3-12 | Example of ATPG Circuit                            | . 39 |

| Figure 3-13 | Commands for Programmable Algorithm Function       | . 39 |

| Figure 3-14 | The Example Loop Test Waveform                     |      |

| Figure 3-15 | Example of Retention Time Option in testbech.v     | . 45 |

| Figure 3-16 | Implementation of Bypass Circuit by Wire           | . 47 |

| Figure 3-17 | Implementation of Bypass Circuit by Register       | . 47 |

| Figure 3-18 | Example of Register Sharing                        | . 48 |

|             |                                                    |      |

## **EZ-BIST User Manual v3.3**

| Figure 3-19 | Clock Architecture of clock_function_hookup Option  | 49 |

|-------------|-----------------------------------------------------|----|

| Figure 3-20 | Clock Architecture of clock_switch_of_memory Option | 49 |

| Figure 3-21 | Diagnosis Fail Memory Information                   | 50 |

| Figure 3-22 | Diagnosis Fail Time Information                     | 50 |

| Figure 3-23 | Default Algorithm Function Block                    | 52 |

| Figure 3-24 | select_elem_testing                                 | 53 |

| Figure 3-25 | Select Testing Elements Sub Function Block          | 54 |

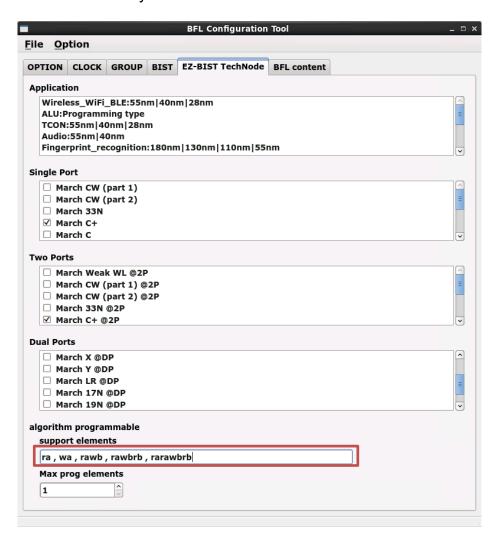

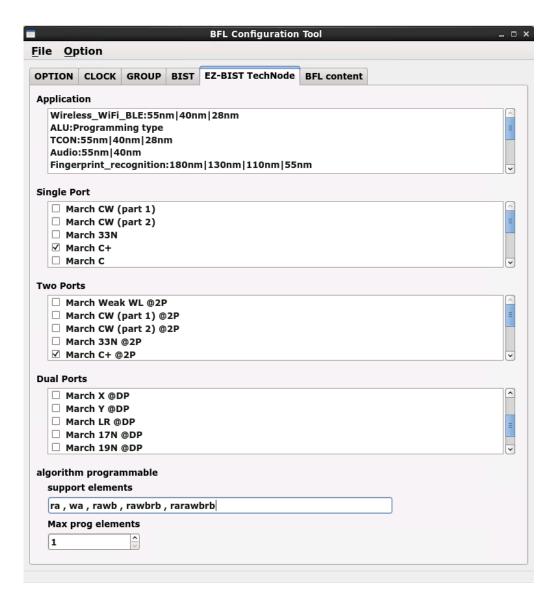

| Figure 3-26 | BFL TechNode                                        | 56 |

| Figure 3-27 | BFL Setting File                                    | 57 |

| Figure 3-28 | Run the BFL Setting File                            | 58 |

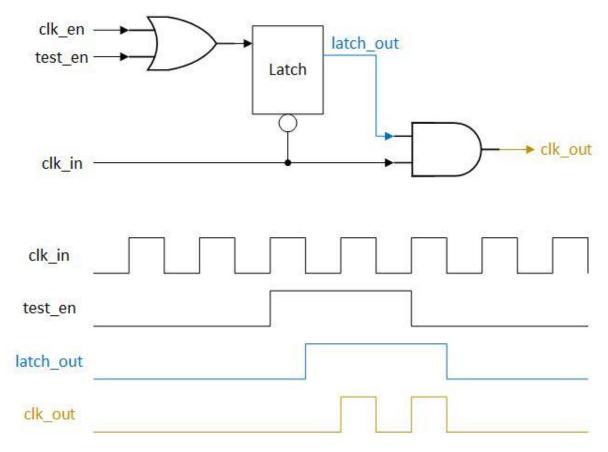

| Figure 4-1  | Clock Gating Logic for Simulation and Synthesis     | 65 |

| Figure 4-2  | Clock Gating Cell with Waveform                     | 65 |

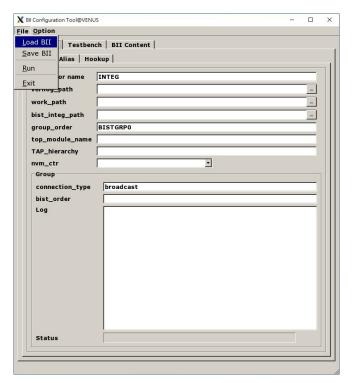

| Figure 5-1  | Load BII                                            | 66 |

| Figure 5-2  | Options of Integrator Function Block                | 67 |

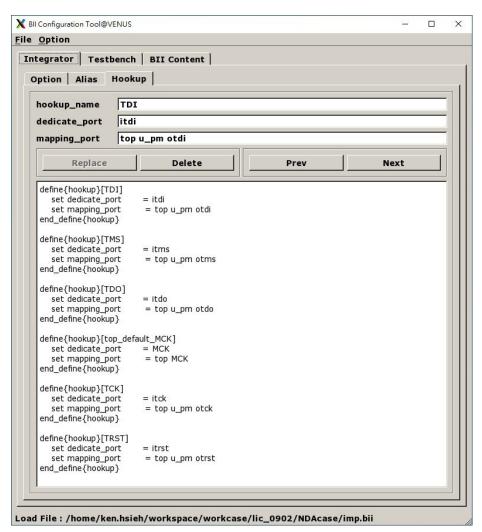

| Figure 5-3  | Hookup Sub Function Block                           | 70 |

| Figure 5-4  | BII File Hookup Information Table in *.integ File   | 71 |

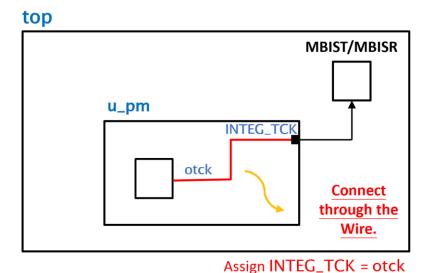

| Figure 5-5  | The Example of Port Connection                      | 72 |

| Figure 5-6  | The Example of Wire Connection                      | 73 |

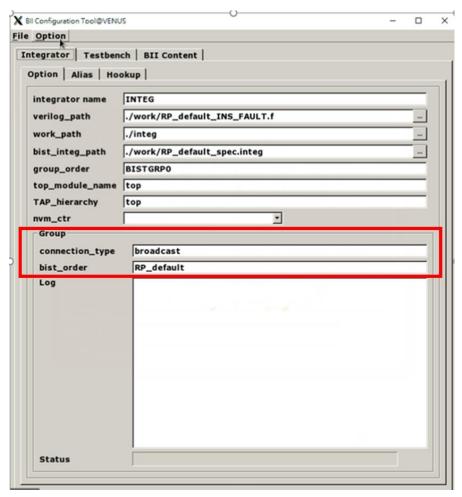

| Figure 5-7  | Group Sub Function Block                            | 74 |

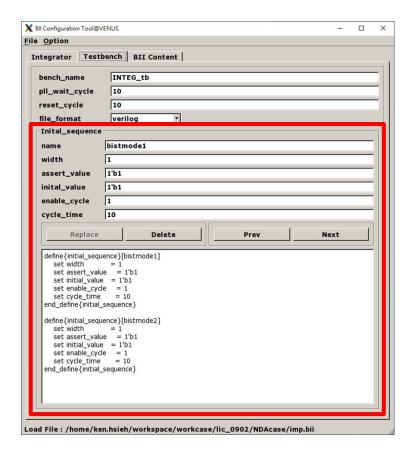

| Figure 5-8  | Testbench Function Block                            | 76 |

| Figure 5-9  | Initial_sequence Sub Function Block                 | 77 |

| Figure 5-10 | Example of BII Setting Content                      | 78 |

| Figure 5-11 | Run BII Setting File                                | 79 |

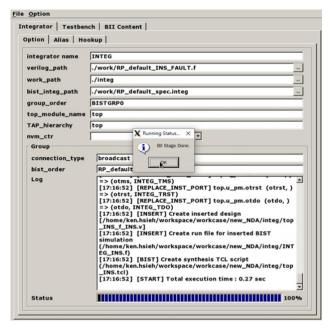

| Figure 5-12 | The Status Window When BII Flow is Completed        | 79 |

## List of Tables

| Table 1-1  | EZ-BIST Features                                    | 1  |

|------------|-----------------------------------------------------|----|

| Table 1-2  | EZ-BIST Input Files                                 | 2  |

| Table 1-3  | EZ-BIST Output Files                                | 2  |

| Table 3-1  | Clock Information                                   | 27 |

| Table 3-2  | Commands for Programmable Algorithm                 | 40 |

| Table 3-3  | BG Field Definition                                 | 42 |

| Table 3-4  | Example of Bit Inverse                              | 42 |

| Table 3-5  | Example of Column Inverse                           | 43 |

| Table 3-6  | Example of User-defined Background and Test Pattern | 44 |

| Table 3-7  | Supported Units of Retention Time                   | 46 |

| Table 3-8  | Fixed Four Memory Address                           | 51 |

| Table 3-9  | Fixed Two Memory Address                            | 51 |

| Table 3-10 | Format of March CW Element                          | 55 |

| Table 4-1  | Self-MBIST Related Files                            | 59 |

| Table 4-2  | Insert MBIST Related Files                          | 60 |

| Table 4-3  | Generated Folder                                    | 61 |

| Table 4-4  | Commands of Makefile                                |    |

| Table 6-1  | Testing Algorithms for SRAM in EZ-BIST              | 81 |

| Table 6-2  | Testing Algorithms for ROM in EZ-BIST               | 83 |

| Table 6-3  | The Default Setting of BFL file                     | 84 |

| Table 6-4  | Synthetic Area of default.bfl                       | 85 |

| Table 6-5  | Area Comparison Table                               | 87 |

## Type conversion in this document

| Conversion    | Meaning for use                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------|

| Bold          | Items in the user interface that you select or click and text that you type into the user interface |

| talic         | Variables in commands, code syntax, and path names                                                  |

| Courier       | File name                                                                                           |

| 4639          | Emphasize the meaning                                                                               |

| Color in blue | The outputs from EZ-BIST tool presenting in blue color                                              |

|               | Omitted material in a line of code                                                                  |

| <u>:</u>      | Omitted lines in code and report examples                                                           |

| []            | Optional items in syntax descriptions to specify                                                    |

| ()            | Explanations or to clarify meaning                                                                  |

| {}            | Repeatable items in syntax descriptions                                                             |

|               | Separated the individual item in syntax descriptions                                                |

### 1. Introduction to EZ-BIST

EZ-BIST is an EDA tool that can generate the test circuit for MBIST (Memory Built-In Self-Test), providing total solutions including comprehensive test algorithms, autogrouping mechanism, and auto-integration mechanism for MBIST circuits and the original circuit. It is easy for users to generate optimized MBIST circuits.

#### 1.1. Features

As shown in Table 1-1, EZ-BIST supports several features. For more details, please refer to <u>Application Notes</u>.

**Table 1-1 EZ-BIST Features**

| Feature |                                             | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| РОТ     | Power_On-Test                               | It is used to guarantee that memory can execute normally after powered on, EZ-BIST supports the POT function for users to implement the POT design.                                                                                                                                                                                                                                  |

| ACT     | Auto-Clock<br>Tracing                       | ACT can trace the clock root to the clock source of memory modules and classify those memories into different clock domains. This mechanism not only saves time of connecting clock sources manually but also helps users to trace the clock in an easier way during creating MBIST.                                                                                                 |

| BUF     | Bottom-Up Flow                              | BUF is designed for IP/Harden implementation. Users can insert MBIST in an individual module. Then, integrate these individual modules in the top module.                                                                                                                                                                                                                            |

| AGC     | Auto-Gating<br>Clock Cell<br>Insertion Flow | To reduce power consumption, EZ-BIST supports AGC for users to insert gate cells and MUX in front of MBIST automatically.                                                                                                                                                                                                                                                            |

| DIAG    | Diagnosis<br>Function                       | In general, MBIST only shows the results of pass or fail after MBIST executes memory testing. To analyze memory defects, EZ-BIST supports memory diagnosis to collect related information such as memory failure addresses, failure patterns, etc. In addition to collecting information, EZ-BIST diagnosis can also assign diagnosis buffer sizes and control the diagnosis timing. |

#### 1.2. Architecture

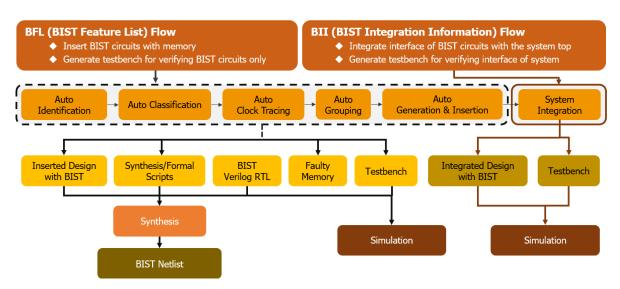

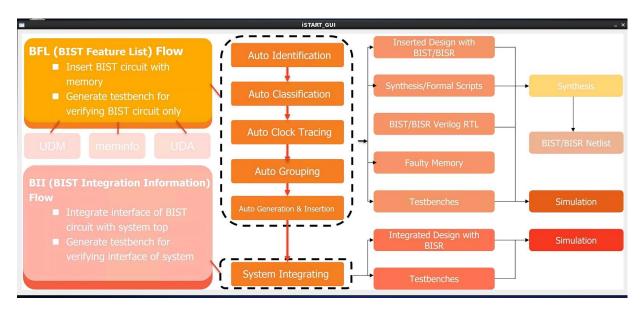

Figure 1-1 shows the operation flow of EZ-BIST.

Figure 1-1 EZ-BIST Operation Flow Diagram

EZ-BIST input files include the files listed below:

Table 1-2 EZ-BIST Input Files

| Top HDL Design | Top HDL design with memory models |

|----------------|-----------------------------------|

| Memory Module  | Verilog files of memory models    |

| UDM Files      | User-defined memory files         |

EZ-BIST output files include the files listed below:

Table 1-3 EZ-BIST Output Files

| Inserted Design      | Integrated MBIST circuits with the top HDL design          |  |

|----------------------|------------------------------------------------------------|--|

| Synthesis Scripts    | Synthesis scripts for users to synthesize                  |  |

| MBIST Verilog Design | Generated MBIST circuits design                            |  |

| Fault Memory         | Generated fault memory models                              |  |

|                      | This is used to verify functional correctness of MBIST and |  |

|                      | circuits with a pre-defined error bit memory.              |  |

| Testbench            | Testbench of MBIST circuits simulation                     |  |

## 2. EZ-BIST Command Options and Parameters

Users can execute EZ-BIST commands with the options, --help or -h, to know all the options supported by EZ-BIST. Figure 2-1 shows an example of executing EZ-BIST with option -h and this chapter will introduce these options. The upper section is the command list. The lower section is the command descriptions.

```

usage: ezBist [-h] [-bii INTEGRATE FILE] [-bfl BFL FILE]

[-f RUN_FILE [RUN_FILE ...]] [-v VERILOG_FILE [VERILOG_FILE ...]]

[-W DIR] [-top MODULE] [-I] [--genmeminfo]

[-integ FILE [FILE ...]] [-u FILE [FILE ...]] [-pm Verilog type]

[--integrator] [--faultfree] [--ug UDM FILE config FILE]

[--rcfg Addr length Data width output FILE] [--tempgen]

[--memchecker] [--memlib2udm MEMLIB_FILE]

[--bflconfig [BFL FILE]] [--biiconfig [BII FILE]]

[--pathconv work path] [--STILloopformat work path]

[--latchgo_hier latchgo_data meminfo] [--udmgui [UDMGUI]]

[--meminfogui [MEMINFO]]

optional arguments:

-h, --help

show this help message and exit

-bii INTEGRATE FILE

input BII file

-bfl BFL FILE

input BFL file

-f RUN FILE [RUN FILE ...]

input run file(s)

-v VERILOG FILE [VERILOG FILE ...] input 4 verilog file(s)

-W DIR

specify working path

-top MODULE, -T MODULE

specify top module

insert BIST to design

-I, --insert

```

Figure 2-1 EZ-BIST Command Options

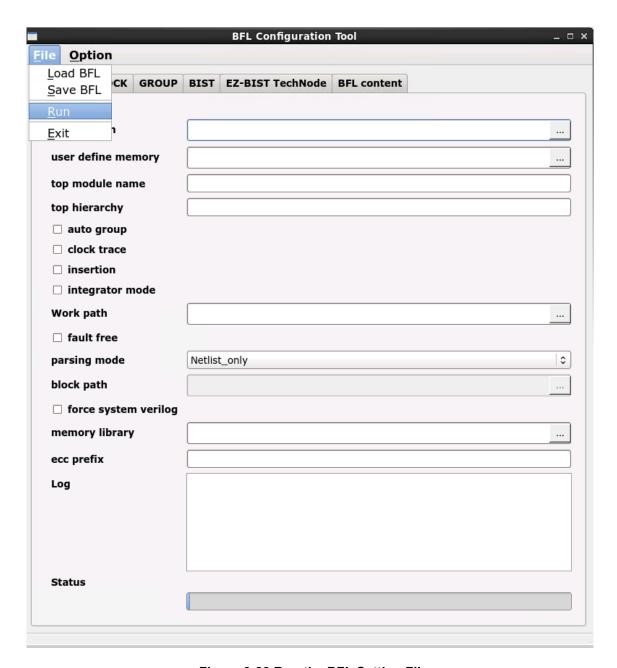

#### 2.1. Invoke EZ-BIST with the GUI Mode

**Usage:** --gui

**Description:** This option is used to invoke EZ-BIST with the GUI mode.

**Example:** \$ ezBist --gui

Figure 2-2 EZ-BIST GUI Mode

#### 2.2. Input Verilog Files

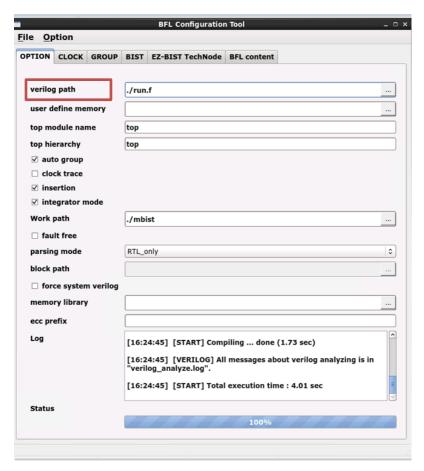

Figure 2-3 Verilog File Path

**Usage:** -v [VERILOG\_PATH]

**Description:**

This option specifies the paths of Verilog design files. The design files here include "system design files" and "memory models". EZ-BIST provides an auto-insertion function to integrate MBIST circuits into the original system design. For this reason, users need to provide the whole design files rather than the memory files only.

This option supports either reading one Verilog file or reading all files in the working directory. It also supports the file-list file format  $\star$  . f. Users can integrate all design files into a single file-list file and read it through EZ-BIST commands. EZ-BIST will read design files automatically. The file-list file also supports +define+, +incdir+, and the -y options.

**Example 1:** \$ ezBist -v vlog\_1

EZ-BIST will read the Verilog files in vlog 1 directory.

**Example 2:** \$ ezBist -v vlog\_1/file1.v vlog\_2/file4.v

EZ-BIST will read the file1.v in vlog\_1 directory and file4.v

in vlog\_2 directory.

**Example 3:** \$ ezBist -v filelist.f

EZ-BIST will read the designs in fielist.f. Figure 2-4 is an

example of the file-list file.

```

-v ./memory/rf_2p_24x28.v

-v ./memory/sram_sp_4096x64.v

-v ./memory/rom_6144_64.v

-v ./memory/rf_sp_128x22.v

-v ./memory/sram_dp_1024x64.v

-v ./memory/sram_sp_24x56.v

-v ./memory/sram_sp_2048x64.v

-v ./memory/sram_sp_640x32.v

-v ./memory/rf_2p_64x64.v

-v ./memory/rf_2p_72x14.v

-v ./memory/sram_sp_1024x32.v

-v ./memory/RA1RW_D2048_W128_BE_RE.v

-v ./memory/RA1RW_D2048_W140_BE_RE.v

-v ./memory/RA1RW_D1024_W128_BE_RE.v

```

Figure 2-4 File-list File Example

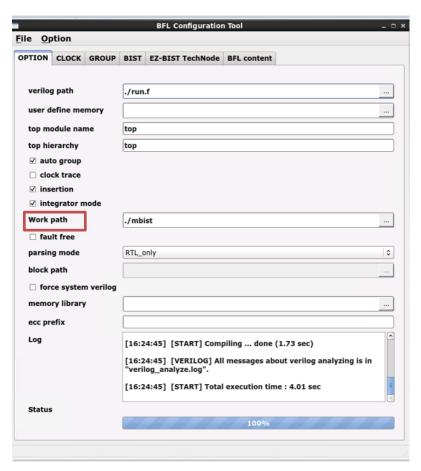

#### 2.3. Specify the Working Path

Usage: -W [WORK\_PATH]

**Description:** This option is for setting the output directory of EZ-BIST execution

results.

**Example 1:** \$ ezBist -v [VLOG\_PATH]/[file\_1].v -W [WORK\_PATH]

EZ-BIST will read the file 1.v design file and save output results

into WORK\_PATH.

**Example 2:** \$ ezBist -v [VLOG\_PATH]/[file\_1].v

Without the -W option, EZ-BIST will save all generated results into

the current working directory.

Figure 2-5 Work Path

#### 2.4. Auto-Identify the Memory Model

**Usage:** --memchecker

**Description:** This option is used to execute EZ-BIST memory checker to identify

memory models defined by users with the -v option.

**Example:** \$ ezBist --memchecker -f filelist.f

Users can check if there is a memory model that cannot be

identified by reviewing the output messages as Figure 2-6.

#### Input file(s): [1] /home /workspace/project/memchecker/memory/rom 6144 64.v [2] /home//workspace/project/memchecker/memory/rf 2p 24x56.v [3] /home//workspace/project/memchecker/memory/sram sp 4096x64.v [4] /home//workspace/project/memchecker/memory/sram sp 640x32.v [5] /home//workspace/project/memchecker/memory/sram\_sp\_2048x64.v [6] /home//workspace/project/memchecker/memory/rf 2p 72x14.v [7] /home//workspace/project/memchecker/memory/RA1RW D2048 W140... [8] /home//workspace/project/memchecker/memory/RA1RW D2048 W128... [9] /home//workspace/project/memchecker/memory/sram sp 1024x32.v [10] /home//workspace/project/memchecker/memory/rf\_sp\_128x22.v [11] /home//workspace/project/memchecker/top.v [12] /home//workspace/project/memchecker/memory/sram dp 1024x64.v [13] /home//workspace/project/memchecker/memory/RA1RW\_D1024\_W128... [14] /home//workspace/project/memchecker/memory/rf\_2p\_24x28.v [15] /home//workspace/project/memchecker/memory/rf\_2p\_64x64.v Valid file(s): [1] /home//workspace/project/memchecker/memory/rom\_6144\_64.v [2] /home//workspace/project/memchecker/memory/rf 2p 24x56.v [3] /home//workspace/project/memchecker/memory/sram sp 4096x64.v [4] /home//workspace/project/memchecker/memory/sram sp 640x32.v [5] /home//workspace/project/memchecker/memory/sram\_sp\_2048x64.v [6] /home//workspace/project/memchecker/memory/rf 2p 72x14.v [7] /home//workspace/project/memchecker/memory/RA1RW D2048 W140 BE RE.v [8] /home//workspace/project/memchecker/memory/RA1RW D2048 W128 BE RE.v [9] /home//workspace/project/memchecker/memory/sram sp 1024x32.v [10] /home//workspace/project/memchecker/memory/rf sp 128x22.v [11] /home//workspace/project/memchecker/memory/sram dp 1024x64.v [12] /home//workspace/project/memchecker/memory/rf\_2p\_24x28.v [13] /home//workspace/project/memchecker/memory/rf 2p 64x64.v Unrecognized file(s): [1] /home//workspace/project/memchecker/top.v

Figure 2-6 Memchecker Information

#### 2.5. The Generate the ROM Signature

**Usage:** --memchecker

**Description:** This option is used to execute the EZ-BIST memory checker to

generate a golden ROM signature with the -v [ROM memory RTL

code file] option.

**Example:** \$ ezBist --memchecker -v [ROM memory RTL code file]

Users can verify the signature created by the MBIST and compare

with the golden one.

\$ ezBist --memchecker -v rom\_6144\_64.v

**Note:** The value of a signature will be saved in the

$*\_gold\_signature.txt$  file (see Figure 2-7) and in the meantime, a top.v file will be generated and replaced the

previous one in the memory folder.

rom 6144\_64\_verilog gold\_signature = 7be4eb

Figure 2-7 The Example of \*\_gold\_signature.txt

#### 2.6. Template File Generator

**Usage:** --tempgen

**Description**: This option is used to generate a template file of EZ-BIST. These

template files include BII (MBIST Integration Information) files, BFL (MBIST Feature List) files, UDM files, and PGF files as Figure 2-8.

**Example:** \$ ezBist --tempgen

[ezBist][TEMPLATE] ezBist template generator:

- 1. BIST Feature List (BFL)

- 2. BIST Integration Information (BII)

- 3. User defined memory

- 4. Pattern Gen File (PGF)

- 5. Quit

[ezBist][TEMPLATE] Select an option (Enter ':q' to quit):

Figure 2-8 EZ-BIST Template Generator

#### 2.7. Input BFL File

Usage: -bfl BFL\_FILE

**Description:** This option is used to define a BFL file for EZ-BIST.

**Example:** \$ ezBist -bfl [filename].bfl -W [WORK\_PATH]

After executing this command, EZ-BIST will base on the parameter setting in the <code>[filename].bfl</code> file to generate MBIST related

files into WORK PATH.

#### 2.8. Insert MBIST to Design

Usage: -l, --insert

**Description:** This option is used to integrate the generated MBIST circuits into

the original system designs. Users need to define a top module

name with the -top option when using this option.

**Example:** \$ ezBist -I -top [TOP\_MODULE] -v [VLOG\_PATH]/[file\_1].v

#### 2.9. Specify Top Module

**Usage**: -top [TOP\_MODULE]

**Description:** This option is used to integrate the generated MBIST circuits into the

original system designs. Users need to define a top module name

with the -top option when using this option.

**Example:** \$ ezBist -I -top [TOP\_MODULE] -v [VLOG\_PATH]/[file\_1].v

Figure 2-9 Top Module Name

#### 2.10. Disable Clock Tracing

**Usage:** -N, --disabletracedclk

**Description:** This option is used to disable the clock tracing function of EZ-BIST.

The default setting is "enabled".

\$ ezBist -N -I --top [TOP\_MODULE] -f file\_list.f **Example:**

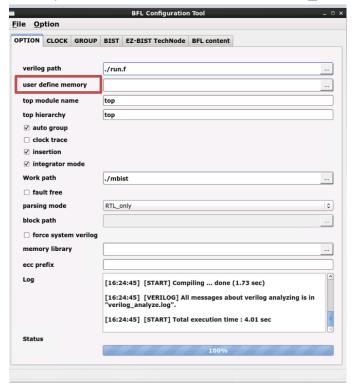

#### 2.11. Input UDM File

Usage: -u UDM FILE

**Description:** This option is used to read the UDM files generated by users. Users

> can generate UDM files when EZ-BIST cannot identify memory models automatically. To edit a UDM file, please refer to Application

Notes for details.

**Example:** \$ ezBist -bfl [filename].bfl -u \*.udm -W [WORK\_PATH]

EZ-BIST will read BFL files and UDM files in the working directory.

The output results will be saved into WORK PATH.

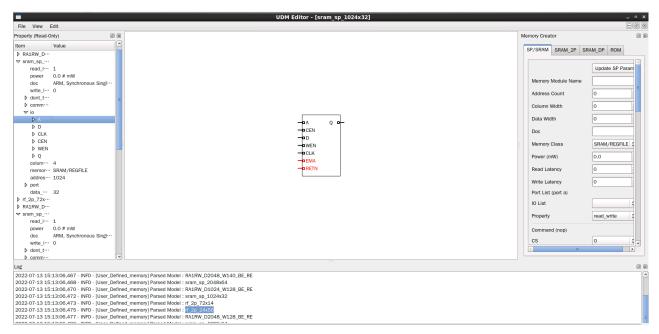

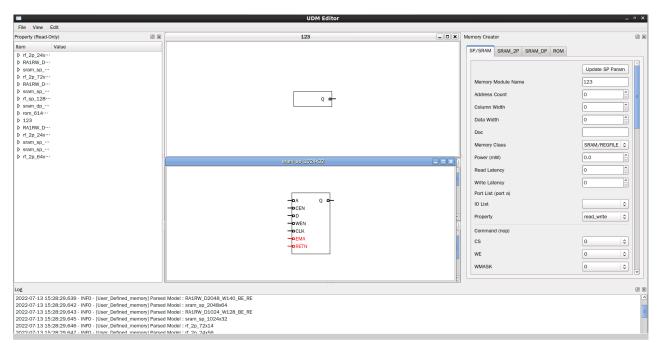

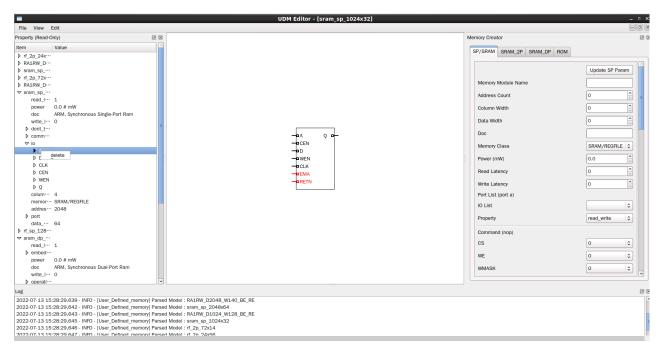

Figure 2-10 User Defined Memory

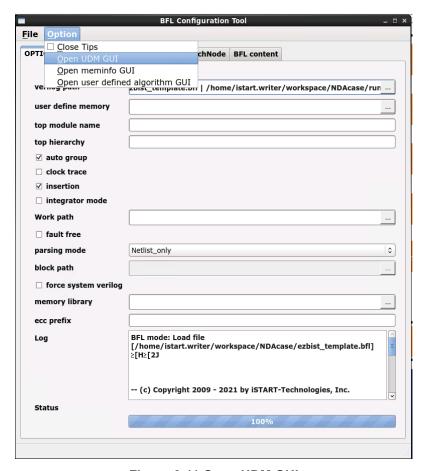

#### 2.12. Generate UDM File in GUI Mode

User can choose Open UDM GUI directly from BFL GUI.

Figure 2-11 Open UDM GUI

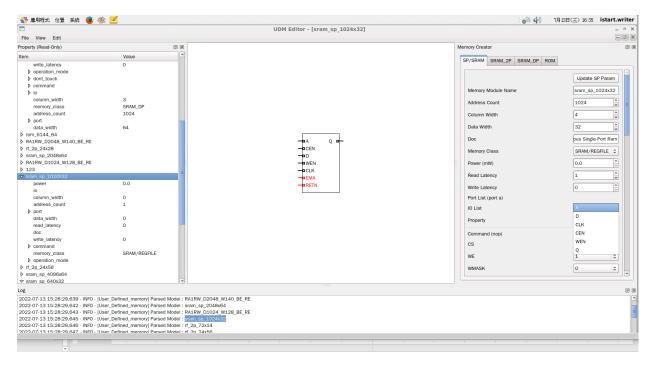

Figure 2-12 Support Batches Adding and Multiple Formats

Set the parameters below through GUI:

- Memory basic parameter

- Port read/write behavior

- Test Port

- IO Port, Don't Touch Port, Repair Port

Figure 2-13 Memory Parameter Settings

(For the detailed information, please refer to Chapter 10 in Application Notes)

Figure 2-14 IO Editing through EZ-BIST

Figure 2-15 IO Adding Rapidly Using Drag & Drop

Figure 2-16 Delete IO with Right Click

```

set width end_define{io}

define{module}[sram sp 1024x32]

ine(module)[sram sp 1024x32]

set address count = 1024

set column width = 4

set data_width = 32

set doc = ARM, Synchronous Single-Port Ram

set memory_class = SRAM/REGFILE

set power = 0.0 # mW

set read_latency = 1

define(io)[0]

set alias = 0

set hold time = 0 # ns

set mux = no

set property = 0

set type = output

set width = 32

end define{io}

define{port}[porta]

set io_list = A,CEN,CLK,D,Q,WEN

set property = read_write

end_define{port}

define{io}[A]

set alias = A

set hold_time = 0 # ns

set mux = yes

set property = ADDR

set type = input

set width = 10

define{dont_touch}[RETN]

set alias = RETN

set force_to = 1

set type = input

set width = 1

end_define{io}

define{io}[D]

set alias = D

set hold_time = 0 # ns

set mux = yes

set property = D

set type = input

set width = 32

end_define{dont_touch}

define{command}[read]

set CS = 0

set WE = 1

end define{io}

end_define{command}

define{io}[CLK]

define{command}[write]

set active = 1

set alias = CLK

set hold_time = 0 # ns

set mux = no

set CS = 0

set WE = 0

end_define{command}

```

Figure 2-17 User Define Memory Generation

#### 2.13. Integrate Multiple MBIST Circuits

**Usage:** --integrator

**Description:** This option is used to integrate multiple MBIST circuits.

**Example:** \$ ezBist --integrator -bii [filename].bii -W [WORK\_PATH]

EZ-BIST will refer to BII files to integrate multiple MBIST circuits

and save output results into WORK PATH.

#### 2.14. Generate UDM File with Library File

**Usage:** --memlib2udm [filename].memlib

**Description:** This option is used to generate UDM files from memory library files.

**Example 1:** \$ ezBist --memlib2udm sram\_512x8.memlib

EZ-BIST will generate UDM files for memory sram\_512x8.

#### 2.15. Generate UDM File with Configuration File

**Usage:** --ug UDM\_File config\_file

**Description:** This option is used to generate UDM files based on the settings in

the configuration file. The configuration file is used to set different widths for address port and data port. Figure 2-18 shows an example of the configuration file. The first column defines the memory model name, the second column defines the address count, the third column defines data width, and the fourth column

defines mux.

**Example:** \$ ezBist --ug sram\_512x8.udm config.file

EZ-BIST will generate UDM files with the same type as the sram 512x8 memory model but with different data width or address

width.

Figure 2-18 UDM Configuration File Example

#### 2.16. Parsing Type Definition

**Usage:** *-pm, --parsingmode*

**Description:** This option is used to specify the input design type. The supported

types are RTL\_only and Netlist\_only.

**Example:** \$ ezBist -pm Netlist only -v example.v

EZ-BIST will import example.v with the nestlist format.

#### 2.17. Fault Free

**Usage:** --faultfree

**Description:** This option is used to decide whether the generated system

designs include fault memory modes or not. When this option is set, the system designs with and without fault memories will be generated. When this option is not set, only the system designs with fault memories will be generated. The file name will be

[design]\_INS.v.

**Example 1:** \$ ezBist -bfl ezBist \_template.bfl -I -W ./work

EZ-BIST will generate an integrated system design with fault

memory models.

**Example 2:** \$ ezBist -bfl ezBist \_template.bfl -I --faultfree -W ./work

EZ-BIST will generate integrated system designs with and without

fault memory models, respectively.

#### 2.18. RCF Generator

**Usage:** --rcfg address\_length data width output\_file

**Description:** This option is used to generate an example RCF file for ROM

memory model. The content of output RCF file is random.

**Example:** \$ ezBist --rcfg 32 8 example.rcf

EZ-BIST will generate an example RCF file with 32x8 matrix

format.

#### 2.19. STIL Format

**Usage**: *--STILloopformat*

**Description:** Change STIL file into the loop format.

**Example:** \$ ezBist --STILloopformat

EZ-BIST will generate STIL file into loop format.

If there are many repetitive testing commands, using the option will

simplify the testing commands as loop instructions.

## 3. EZ-BIST BFL Options

Users can execute EZ-BIST to generate the MBIST circuits with the BFL flow. This chapter will introduce the setting options in the BFL file.

The definitions of function blocks in BFL file are defined as follows:

define{function}

end\_define{function}

Users can find different options in each function block as below.

#### 3.1. OPTION Function Block

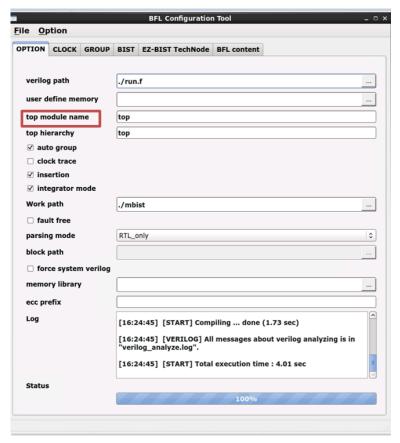

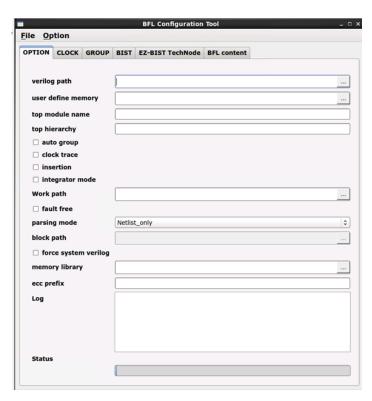

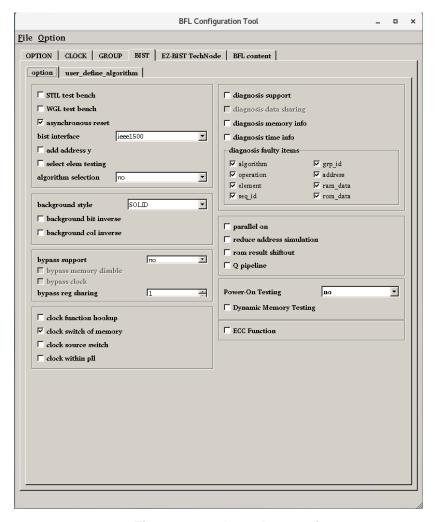

Figure 3-1 shows the parameters in the OPTION function block.

**Figure 3-1 OPTION Function Block**

Argument Option

Description

verilog\_path

User defined

Set the Verilog file paths for EZ-BIST. The format can be set either by  $file1.v \mid file2.v \mid fileN.v$  or file-list file (\* . f).

Note: Each file is separated by a vertical bar "|".

Example:

set verilog\_path = ./top.f

user\_define\_memory

Set UDM file paths for EZ-BIST. The format can be *memory1.udm* | *memory2.udm* | ... | *memoryN.udm*.

User defined

Note: Each file is separated by a vertical bar "|". For more details, please refer to Application Notes.

Example:

set user\_define\_memory = BRAINS.udm

top\_module\_name User defined

Set the top module name of the system design which includes memory modules.

Example:

set top module name = top

top\_hierarchy User defined

Specify the location (instance name) of the controller for MBIST circuits in the design architecture.

Example:

set top\_hierarchy = top

clock trace No, Yes

This option is for users to disable/enable the clock source tracing function. The default setting is "no".

No: Disable the clock source tracing function Yes: Enable the clock source tracing function

| Argument    | Option  |  |

|-------------|---------|--|

| Description |         |  |

| auto_group  | No, Yes |  |

This option is for users to automatically group memory models based on the settings in the GROUP function block. The default setting is "no".

No: Disable the clock auto-grouping function Yes: Enable the clock auto-grouping function

insertion No, Yes

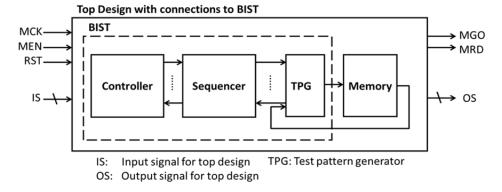

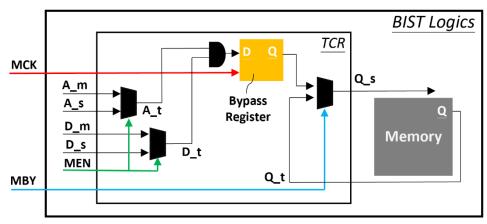

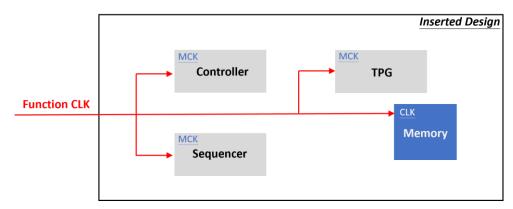

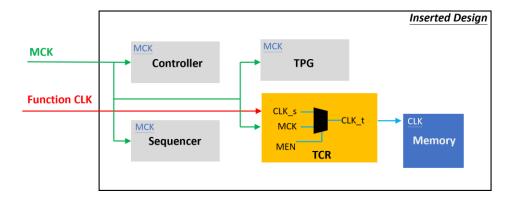

This option is used to integrate the generated MBIST circuits and the original system designs. Figure 3-2 shows the block diagram of the inserted system design.

No: Disable the insertion function Yes: Enable the insertion function

Figure 3-2 Block Diagram of System Design with MBIST Inserted

## integrator\_mode No, Yes

This option is for users to add the dedicated testing port in the top module of MBIST. Because these testing ports adhere to standard protocols such as IEEE 1149.1, users can use the shared pin design to reduce the pin count. The default setting is "no".

No: EZ-BIST will generate some specific hookup pins for the BII flow. Users can use

them to control MBIST or get data from MBIST.

Yes: EZ-BIST will reserve signals internally in advance for testing only in the BFL

flow.

Note: The option must be set to "yes" when clock tracing turns on.

| work_path | User defined |

|-----------|--------------|

|-----------|--------------|

Specify the path for saving the generated results in the BFL flow.

| Argument Option |         |  |

|-----------------|---------|--|

| Description     |         |  |

| fault_free      | No, Yes |  |

When this option is set to "no", EZ-BIST will generate an integrated system design with fault memory models. On the contrary, when this option is set to "yes", EZ-BIST will generate two integrated system designs with and without fault memory. However, the simulation will run on without fault memory. MBIST circuits are integrated into the original system design.

parsing\_mode RTL\_only, Netlist\_only

This option defines the file format of the imported design, supporting RTL\_only and Netlist\_only.

Note: If the Netlist file are not uniquified, the parsing mode must be set to "RLT only."

ecc\_prefix User defined

Specify the prefix of ECC (Error Correction Code) related files.

For example, when this option is set to "ECC", the output repair-related files will be named like ECC [design] INS.v and ECC [filename] tb.v etc.

memory\_library User defined

Define the memory library (shown in example 1), or the memory library file list (shown in example 2) will make EZ-BIST to load the information of memory models.

Example 1: set memory library = /home/workspace/ram1024x32.lvlib

Example 2: set memory library = ./mem lib.f

block\_path User defined

While the design is implemented with the bottom-up flow to insert MBIST into the sub module, it will generate a \*.blockinfo file in the sub module.

Example:

set block path = ./block1/START block1.blockinfo | ./block2/START block2.blockinfo

force system verilog No, Yes

The parsing format will be changed to System Verilog when users set the option to "yes". The default setting is "no".

No: Initial parsing format is Verilog.

Yes: Changed parsing format to System Verilog.

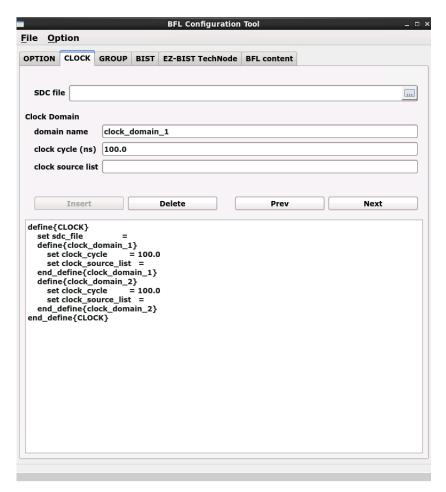

#### 3.1.1. CLOCK Sub Function Block

Users can define the information of clock domain or provide an SDC file for EZ-BIST to do clock tracing.

**Figure 3-3 Clock Sub Function Block**

**Table 3-1 Clock Information**

| Argument                                                            | Option       |  |

|---------------------------------------------------------------------|--------------|--|

| Description                                                         |              |  |

| sdc_file                                                            | User defined |  |

| Specify the path of an SDC file.                                    |              |  |

| define{clock_name}                                                  | User defined |  |

| Set the clock domain name.                                          |              |  |

| clock_cycle                                                         | User defined |  |

| Set the operating period of clock domain defined in "clock_name".   |              |  |

| clock_source_list                                                   | User defined |  |

| Set the source pin or port of clock domain defined in "clock_name". |              |  |

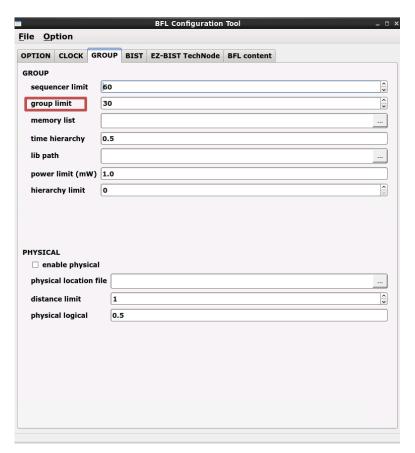

#### 3.1.2. GROUP Sub Function Block

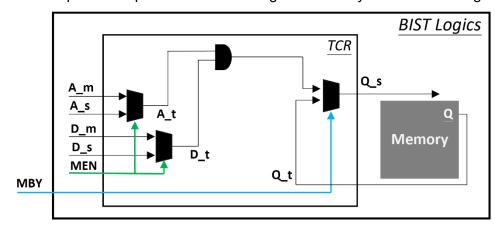

EZ-BIST assigns memory grouping according to the rule of clock domains, types of memory models, the criteria of grouping specifications, and power consumption. Users can also do memory grouping manually based on their own project requirements by editing the memory information file \*.meminfo. Memory models in the same group can be tested in parallel to reduce the testing time.

Each memory will have the dedicated Sequencer ID (SEQ\_ID) and Group ID (GRP\_ID). Memories have the same SEQ\_ID and GRP\_ID are in the same group and can be tested at the same time.

The SEQ\_ID is classified by types, specifications, and the clock domains of memory models. This ID means which sequencer the memory models belong to. The GRP\_ID is classified by power consumption and number limitations of a single group.

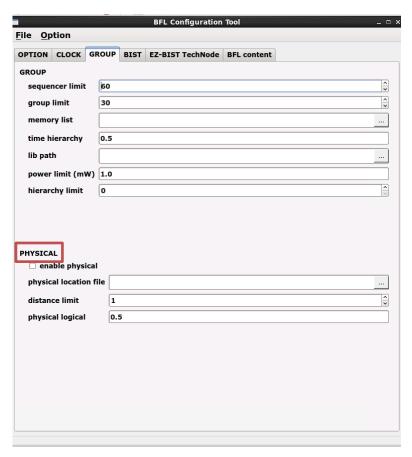

**Figure 3-4 Group Function Block**

| Argument                                                                                                                                                                                                                                    |                                                    | Option                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                 |                                                    |                                                                                            |

| sequencer_limit                                                                                                                                                                                                                             |                                                    | User defined                                                                               |

| This option defines the maximum amount of memory instances in a sequencer.                                                                                                                                                                  |                                                    |                                                                                            |

| Default Value: 60                                                                                                                                                                                                                           |                                                    |                                                                                            |

| group_limit                                                                                                                                                                                                                                 |                                                    | User defined                                                                               |

| This option is used to define the maximum amount of memory instances in a group. This number should be less than the value of <b>sequencer_limit</b> .  Default Value: 30                                                                   |                                                    |                                                                                            |

| memory_list                                                                                                                                                                                                                                 |                                                    | User defined                                                                               |

| Specify the paths of memory info file (*.meminfo). Figure 3-8 is an example of memory info file.                                                                                                                                            |                                                    |                                                                                            |

| For more details, please refer to Application Notes.                                                                                                                                                                                        |                                                    |                                                                                            |

| lib_path                                                                                                                                                                                                                                    |                                                    | User defined                                                                               |

| This option is for users to set the path of memory libraries. EZ-BIST will load power information of memory models from *.lib files and do memory grouping automatically based on the power criteria through the <b>power_limit</b> option. |                                                    |                                                                                            |

| time_hierarchy                                                                                                                                                                                                                              |                                                    | 0 (time) <= value <= 1 (hierarchy)                                                         |

| This option is for users to adjust the weight between the testing time and design hierarchy. The default value is 0.5.                                                                                                                      |                                                    |                                                                                            |

| For example:<br>set time_hierarchy = 0                                                                                                                                                                                                      |                                                    | ssign memory grouping based on the optimized he testing time will be the highest priority. |

| set time_hierarchy = 1                                                                                                                                                                                                                      | EZ-BIST will<br>relationships.<br>In this case, th | assign memory grouping by hierarchy ne logical hierarchy will be the highest priority.     |

| power_limit                                                                                                                                                                                                                                 |                                                    | User defined                                                                               |

| Set the maximum limitation  For example:  set power_limit = 0.005                                                                                                                                                                           | n of power consu                                   | umption in one group.                                                                      |

Note: The unit is mW and can be decimal.

| Argument                                                                                                                                                                                             | Option       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Desc                                                                                                                                                                                                 | cription     |

| hierarchy_limit                                                                                                                                                                                      | User defined |

| Set the maximum hierarchy number when doing auto-grouping. If the hierarchy number between memory models is larger than this number, EZ-BIST will not group these memory models into the same group. |              |

| Default Value: 0 (no limitation of hierarchy                                                                                                                                                         | number)      |

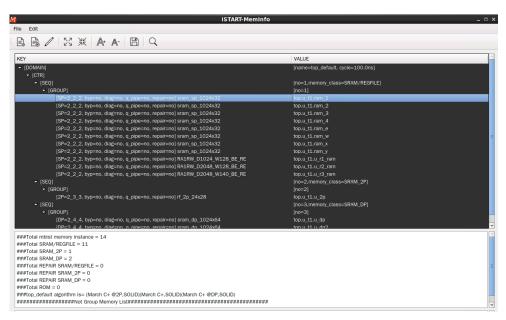

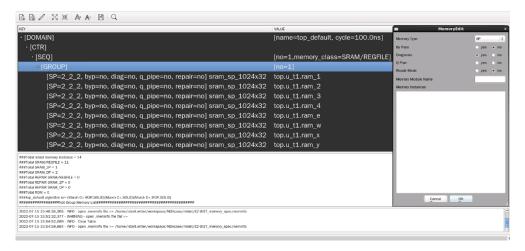

As shown in Figure 3-5, users can open a memory info file by clicking the "File" menu and selecting "Open".

Figure 3-5 Open Memory Info File

Figure 3-6 is an example of the memory info file. For the detailed information, please refer to Chapter 7 in <u>Application Notes</u>.

Figure 3-6 Example of Memory Info File

As shown in Figure 3-7, users can right click "GROUP" and select "add mem" to add memories by batches according to the information described below.

Figure 3-7 Support Batches Adding and Multiple Formats

A memory info file includes the following items. For the detailed information, please refer to Chapter 7 in <u>Application Notes</u>.

- Clock domain: It shows "memory clock domain name" and "testing clock cycle".

- Memory module: It shows the "memory module name" and "memory hierarchy".

- **Bypass**: Set the values of the bypass function.

- Diagnosis: Set the values of the diagnosis function.

- **Q pipeline**: Set the value of the Q pipeline option.

- Group Architecture: This option shows the grouping architecture information including the controller, sequencer, and group.

- Design information: This option shows the number of memory instances, memory types, and testing algorithms.

**Figure 3-8 Memory Info Setting Information**

## 3.1.3. PHYSICAL Sub Function Block

Figure 3-9 PHYSICAL Sub Function Block

(For the detailed information, please refer to the table in the next page.)

| Argument                                                                                                                                                                                                                                                                     |                                               | Option                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                                                                                                                                                                                                                                                  |                                               |                                                                                                                                                                                 |

| enable_physical                                                                                                                                                                                                                                                              |                                               | No, Yes                                                                                                                                                                         |

| If this option is set to "yes", Information) file.                                                                                                                                                                                                                           | EZ-BIST will aut                              | to-group based on the DEF (Design Physical                                                                                                                                      |

| physical_location_file                                                                                                                                                                                                                                                       |                                               | User defined                                                                                                                                                                    |

| Set the paths of the DEF file                                                                                                                                                                                                                                                | <del></del><br><del>)</del> .                 |                                                                                                                                                                                 |

| controller_scope                                                                                                                                                                                                                                                             |                                               | User defined                                                                                                                                                                    |

| After editing a SCOPE file, set the path of the SCOPE file. The scope information should be included with a controller name and position coordinate as follows.  Controller Name Position Coordinate (x1 y1) (x2 y2)  For example, top_default (10000 10000) (300000 400000) |                                               |                                                                                                                                                                                 |

| physical_logical                                                                                                                                                                                                                                                             |                                               | 0 <= value <= 1                                                                                                                                                                 |

| This option is to adjust the witime_hierarchy option.  For example:  set physical_logical = 0                                                                                                                                                                                | EZ-BIST will ca                               | hysical coordinates and values defined in the alculate the number of intermediates based algorithm. Memory models which are located nediate number will be merged into the same |

| set physical_logical = 1                                                                                                                                                                                                                                                     | group. EZ-BIST will ex of the <b>time_hie</b> | recute memory grouping based on the value rarchy option.                                                                                                                        |

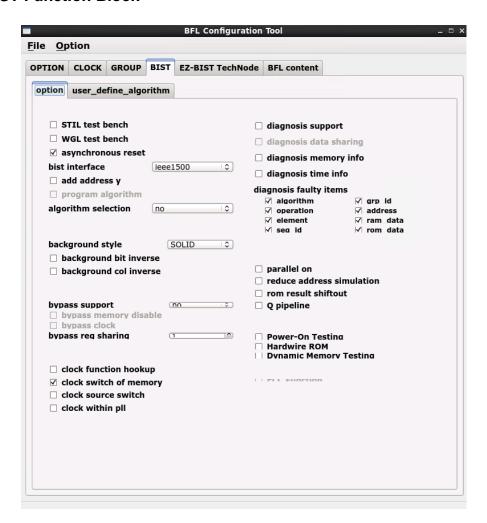

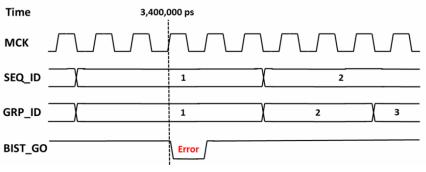

#### 3.2. BIST Function Block

Figure 3-10 MBIST Function Block

| Argument                                                                                                                                                                                                                                                                                                                                                               | Option  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Descript                                                                                                                                                                                                                                                                                                                                                               | ion     |

| STIL_test_bench                                                                                                                                                                                                                                                                                                                                                        | No, Yes |

| Generate a test pattern with the STIL format (IEEE 1450-Standard Test Interface Language) for the tester machine when this option set to "yes". Since the result in the default STIL format might be a lot of repeated codes, users can change it into the loop format by using command lines, STILloopformat.  No: Not generate the test pattern with the STIL format |         |

| Yes: Generate the test pattern with the S                                                                                                                                                                                                                                                                                                                              |         |

| Argument       | Option  |

|----------------|---------|

| Description    |         |

| WGL_test_bench | No, Yes |

Generate a test pattern with the WGL format (Waveform Generation Language) when this option is set to "yes".

No: Not generate the test pattern with the WGL format Yes: Generate the test pattern with the WGL format

bist\_interface basic, basicIO, ieee1500, ieee1149.1

Select the MBIST interface.

Note: For more details of these interfaces, please refer to **IO Pin Definition**.

Note: When users set **bist\_interface** to "ieee1149.1", then IEEE 1149.7 will be the output interface.

Note: When users set **bist\_interface** to "ieee1500", then IEEE 1149.1 will be the output interface.

| add_address_y | No, Yes |

|---------------|---------|

|---------------|---------|

This option defines MBIST algorithms and supports the Y direction. The generated testbench supports the X and Y addressing modes (X stands for the row of the memory, and Y stands for the column of the memory.)

No: The MBIST pattern testing only supports the X direction.

Yes: The MBIST pattern testing supports both X and Y directions.

| X_Y = 00                                                                       | Write MBIST pattern in the X direction only.                     |

|--------------------------------------------------------------------------------|------------------------------------------------------------------|

| X_Y = 01                                                                       | Write MBIST pattern the X direction first, and then Y direction. |

| $X_Y = 10$ Write MBIST pattern in the Y direction first, and then X direction. |                                                                  |

| X_Y = 11                                                                       | Write MBIST pattern in the Y direction only.                     |

Note: This option does not support memories with a column width of "0".

Note: To define the X or Y directions, users must modify the X\_Y setting in the testbench file.

| clock source switch   | No, Yes  |

|-----------------------|----------|

| 0.00N_00U.00_01.11011 | 140, 103 |

This option is used to select the testing frequency while the **clock\_within\_pll** option and **clock\_switch\_of\_memory** option is turned on. The MBIST circuit will have a dedicated test input signal named TRANS. Users can use this input signal to choose the testing frequency (from SCK or MCK).

Note: The option must be set to "no" when clock tracing is turned on.

| A                                                                                                                                                                           | 0                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Argument                                                                                                                                                                    | Option                                                                     |

| Descrip                                                                                                                                                                     | tion                                                                       |

| clock_within_pll                                                                                                                                                            | No, Yes                                                                    |

| If this option is set to "yes", the MBIST circuit will have another clock input source, SCK. This signal is used to connect with an ATE (Automatic Test Equipment) machine. |                                                                            |

| Note: The option must be set to "no" when clo                                                                                                                               | ock tracing is turned on.                                                  |

| diagnosis_support No, Yes                                                                                                                                                   |                                                                            |

| This option is used to enable the diagnosis motime and failed memory information.                                                                                           | de, which can provide users with the failure                               |

| No: Disable the Diagnosis mode                                                                                                                                              |                                                                            |

| Yes: Enable the Diagnosis mode                                                                                                                                              |                                                                            |

| diagnosis_data_sharing                                                                                                                                                      | No, Yes                                                                    |

| Users can integrate diagnosis circuits into the to reduce the area of MBIST circuits when this                                                                              |                                                                            |

| diagnosis_faulty_items                                                                                                                                                      | algorithm, operation, element, seq_id, grp_id, address, ram_data, rom_data |

| This option is used to select the output items of the diagnosis result based on the chip failure analysis requirement.                                                      |                                                                            |

| Evenente                                                                                                                                                                    |                                                                            |

**Example**

set diagnosis\_faulty\_items = algorithm, operation, element, seq\_id, grp\_id, address, ram\_data, rom\_data

## rom\_result\_shiftin No, Yes

This option is used to do ROM memory testing and import the signatures for internal verification. The scenario is used when the contents of the ROM memory is not confirmed at the initial development stage.

For example, when users set **rom\_result\_shiftin** to "yes" and the **POT** function is enabled, the testing results of ROM memory will be transferred to the internal circuit via commands.

| rom result   | shiftout | No. Yes   |

|--------------|----------|-----------|

| TOILL LESUIL | Silitout | 1 110. 16 |

This option is used to do ROM memory testing and export the signatures for external verification. The scenario is used when the contents of ROM memory is not confirmed at the initial development stage.

For example, when user set **rom\_result\_shiftout** to "yes" and the testing results of the ROM memory will be transferred to the output interfaces via commands.

| Argument    | Option  |  |

|-------------|---------|--|

| Description |         |  |

| Q_pipeline  | No, Yes |  |

This option is used to add an extra pipeline register to MBIST logics.

No: No extra register will be added to the data output of a memory model.

Yes: An extra register will be added to the data output of a memory model to enhance

operating timing of MBIST logics.

# asynchronous\_reset No, Yes

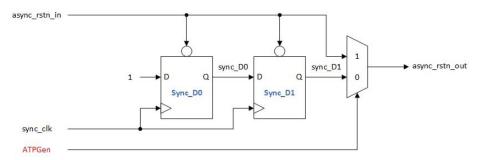

The option is used to specify asynchronous or synchronous reset of MBIST. The circuit can be differentiated into two types, "synchronous reset" and "asynchronous reset". "Synchronous reset" indicates all DFFs are triggered to reset and then reset at the same time. "Asynchronous reset" indicates the reset of the circuit is based on the sequential order. In other word, this is not synchronous reset.

No: Synchronous reset will be applied with two DFFs. In addition, hookup the RSTN port (the MBIST reset signals) and the ATPGen port.

Yes: It indicates the asynchronous reset while one reset signal asserts. Additionally, hookup the RSTN port in the BII flow.

Figure 3-11 shows an example of synchronous/asynchronous circuits. When the ATPGen port is under the "scan mode", the synchronous circuit will be bypassed and be regarded as the asynchronous circuit to select signals.

Figure 3-11 Example of Synchronous/Asynchronous Circuit

| Argument    | Option  |  |

|-------------|---------|--|

| Description |         |  |

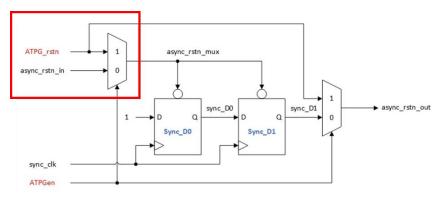

| atpg_reset  | No, Yes |  |

This option is for users to reset the "Automatic Test Pattern Generation". When the option is set to "yes", EZ-BIST tool will string all the reset signals under MBIST into a series of ATPG rstn.

Note: In the BII flow, hookup ATPG rstn and ATPGen ports at the same time.

Note: When users set **atpg\_reset** to "yes", the ATPG signal will be inserted into the multiplexer (MUX) for the selection of ATPG\_rstn or async\_rstn\_in signal as shown in Figure 3-12.

Figure 3-12 Example of ATPG Circuit

select\_elem\_testing No, Yes

This option is for users to do testing with user-defined test algorithms rather than EZ-BIST built-in algorithms by controlling input interfaces. When this function is turned on, users can select the algorithm elements in the SEQ, and the elements can be tested in the testbench.

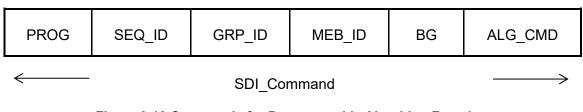

A programmable algorithm is presented as a PROG entry. Figure 3-13 shows the testing commands while this option is turned on. Table 3-2 is the definition of these entries.

Note: User-defined testing algorithms cannot support ROM memory testing and the diagnosis function.

Figure 3-13 Commands for Programmable Algorithm Function

| Table 3-2 Commands for Programmable Algorithm |                                                                                                                                                                                                                         |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                       | Description                                                                                                                                                                                                             |

| PROG                                          | PROG = 0, executing the EZ-BIST built-in algorithm PROG = 1, executing the user-defined algorithm                                                                                                                       |

| SEQ_ID                                        | Sequencer ID of the memory                                                                                                                                                                                              |

| GRP_ID                                        | Group ID of the memory                                                                                                                                                                                                  |

| MEB_ID                                        | Memory ID of the memory                                                                                                                                                                                                 |

| BG                                            | "SOLID" is the default background style. Only when "5A" is chosen, users can select four different modes to test. For more details, please refer to Table 3-3.                                                          |

| ALG_CMD                                       | This ALG_CMD entry is based on March algorithm, users also can define it. While PROG = 1, MBIST circuits will execute user-defined algorithms. The width of the ALG_CMD entry is based on the March element definition. |

|                                                                                                                                                                                  | Argument                          | Option                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|

| Description                                                                                                                                                                      |                                   |                        |

| algorithm_selection No, Outside, Scan                                                                                                                                            |                                   | No, Outside, Scan      |

| This option is for users to choose a single test algorithm or multiple test algorithms to test sequentially.                                                                     |                                   |                        |

| No: Users can select algorithms which will be tested with MBIST circuits sequentially.                                                                                           |                                   |                        |

| Outside: Users can select the test algorithm with the input port ALG and this input port will be added when the basic interface is defined.                                      |                                   |                        |

| Scan:                                                                                                                                                                            | Users can launch a test with IEEE | E 1149.1 or IEEE 1500. |

| algorithm_                                                                                                                                                                       | algorithm_loop_test No, Yes       |                        |

| This option is for users to improve the loop mode testing efficiency. Some tests require a loop mode, but using multiple testing commands can cause delays between the commands. |                                   |                        |

| No: Not support continuous memory testing Yes: Support continuous memory testing                                                                                                 |                                   |                        |

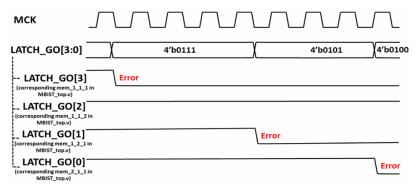

| Users can send commands to control the BURN_IN signal to define the period of testing as Figure 3-14 when this option set to "yes".                                              |                                   |                        |

| BURN_IN                                                                                                                                                                          |                                   |                        |

| ALG[1:0]                                                                                                                                                                         | 0 / 1 / 2 /                       | 3 ( 1 ) 2 ( 3 ) 0      |

Figure 3-14 The Example Loop Test Waveform

| Argument                   | Option |  |  |

|----------------------------|--------|--|--|

| Description                |        |  |  |

| background_style SOLID, 5A |        |  |  |

The type of **background\_style** can be set to "SOLID" and "5A" (Check Board), the contents are defined in the bg table file.

There is an entry named BG (Background) in the SDI\_Command. When **background\_style** is set to 5A, the BG settings are shown as Table 3-3.

Note: If users adopt "March Mdsn1" as an algorithm, **background\_style** cannot be set to "5A".

**Table 3-3 BG Field Definition**

| BG [1:0] | Definition |

|----------|------------|

| 00       | SOLID + 5A |

| 01       | SOLID      |

| 10       | 5A         |

| 11       | SOLID + 5A |

| background_bit_inverse | No, Yes |

|------------------------|---------|

|------------------------|---------|

Bit inverse means that the BG testing data will be inversed by the increasing order or decreasing order of the memory address.

For example, the BG testing data of a 64x8 memory with SOLID BG is shown as Table 3-4.

**Table 3-4 Example of Bit Inverse**

| Memory Address | SOLID BG Test Data | Description               |

|----------------|--------------------|---------------------------|

| 0000_0000      | 0000_0000          | testing data non-inversed |

| 0000_0001      | 1111_1111          | testing data inversed     |

| 0000_0010      | 0000_0000          | testing data non-inversed |

| 0000_0011      | 1111_1111          | testing data inversed     |

|                |                    |                           |

| Argument               | Option  |  |  |

|------------------------|---------|--|--|

| Description            |         |  |  |

| background_col_inverse | No, Yes |  |  |

Column inverse means that the BG testing data will be inversed by the changes of the row memory address. If this changing time is larger than the CIC (Column Inverse Counts) number, the BG testing data will be inversed. The CIC number is defined by the memory Mux value.

For example, a 64x8 memory with Mux = 4 and the BG type = SOLID. The BG testing data is shown as Table 3-5.

**Table 3-5 Example of Column Inverse**

| Memory Address | SOLID BG Test Data | Description               |

|----------------|--------------------|---------------------------|

| 0000_0000      | 0000_0000          | testing data non-inversed |

| 0000_0001      | 0000_0000          |                           |

| 0000_0010      | 0000_0000          |                           |

| 0000_0011      | 0000_0000          |                           |

| 0000_0100      | 1111_1111          | testing data inversed     |

| 0000_0101      | 1111_1111          |                           |

| 0000_0110      | 1111_1111          |                           |

| 0000_0111      | 1111_1111          |                           |

| 0000_1000      | 0000_0000          | testing data non-inversed |

| 0000_1001      | 0000_0000          |                           |

| 0000_1010      | 0000_0000          |                           |

| 0000_1011      | 0000_0000          |                           |

|                |                    |                           |

| Argument                    | Option |  |

|-----------------------------|--------|--|

| Description                 |        |  |

| user_define_bg User defined |        |  |

Users can specify the background test pattern via the setting of user\_define\_bg.

For example, if the width of the data is 4 bits:

Example 1: When users assign **user\_define\_bg** to "3" and **background\_style** to

"SOLID", then the testing pattern will be 0x3.

Example 2: When users assign **user\_define\_bg** to "3" and **background\_style** to

"5A", then the testing pattern will be 0x3,0xC,0x5,0xA.

Table 3-6 lists the example of user-defined background and the corresponding test patterns.

Table 3-6 Example of User-defined Background and Test Pattern

| Background Style | User-defined<br>Background | Test Pattern |

|------------------|----------------------------|--------------|

| SOLID            | 3                          | 3            |

| 5.0              | 3                          | 3, C, 5, A   |

| 5A               | 3, 7                       | 3, C, 7, 8   |

| Argument                  | Option |  |

|---------------------------|--------|--|

| Description               |        |  |