## **EDA** tool isn't so complicated

Technical Support Department Senior Manager TP Hsieh

精彩回顧: https://youtu.be/u\_YwiBEXgJc

#### **Outline**

- ◆技術為根、方便使用為本的設計理念出發

- ◆客製化不是奢華要求,是芯測基本的設計方針

- ◆今天我想來點...技術支持-Delivery Service

- ◆芯測將和你一起走向數位新世代

# 技術為根、方便使用為本的設計理念出發 Intrinsic Advanced Technology, Extrinsic Simple Interface to Design

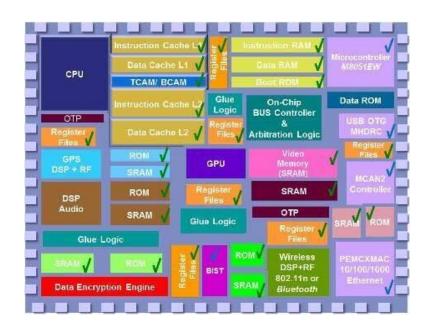

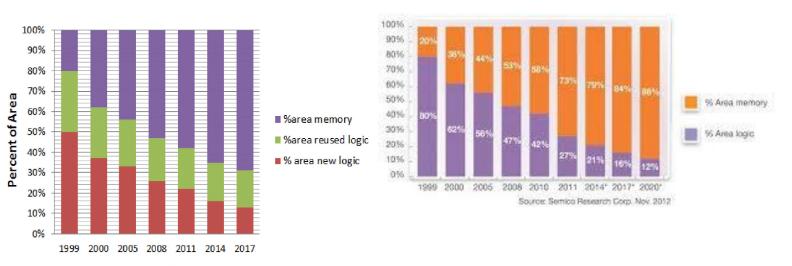

#### **Memory Usage Analysis**

**◆Both memory and logic circuit density show positive growth**

Source: Semico Rsearch Coorporation

**◆**The growth of memory usage are much larger than of logic circuit

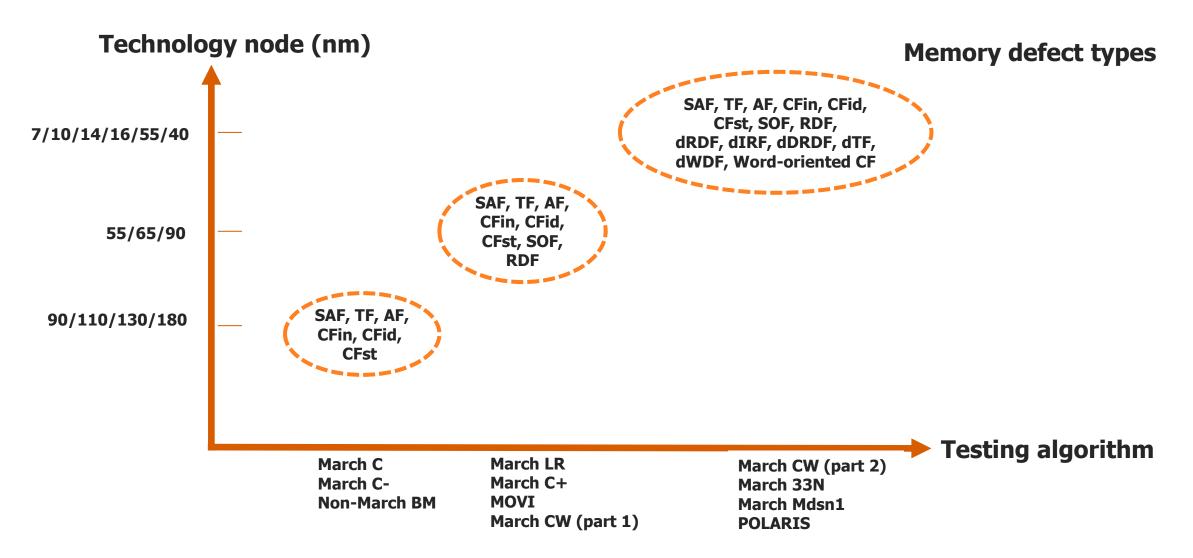

## **Testing Algorithms vs. Technology Node**

#### **Patents**

#### **SRAM Testing and Repairing**

- Test pattern generator for SRAM and DRAM

- ALGORITHM INTERGRATING SYSTEM AND INTEGRATING METHOD THEREOF

- **EMBEDDED TESTING MODULE AND TESTING METHOD THEREOF**

- HYBRID SELF-TEST CIRCUIT STRUCTURE

- Method for Repairing Memory and System Thereof

#### NVM (Non-Volatile Memory) Test and Repair IP

Built-In Self-Repair Method for NAND Flash Memory and System Thereof

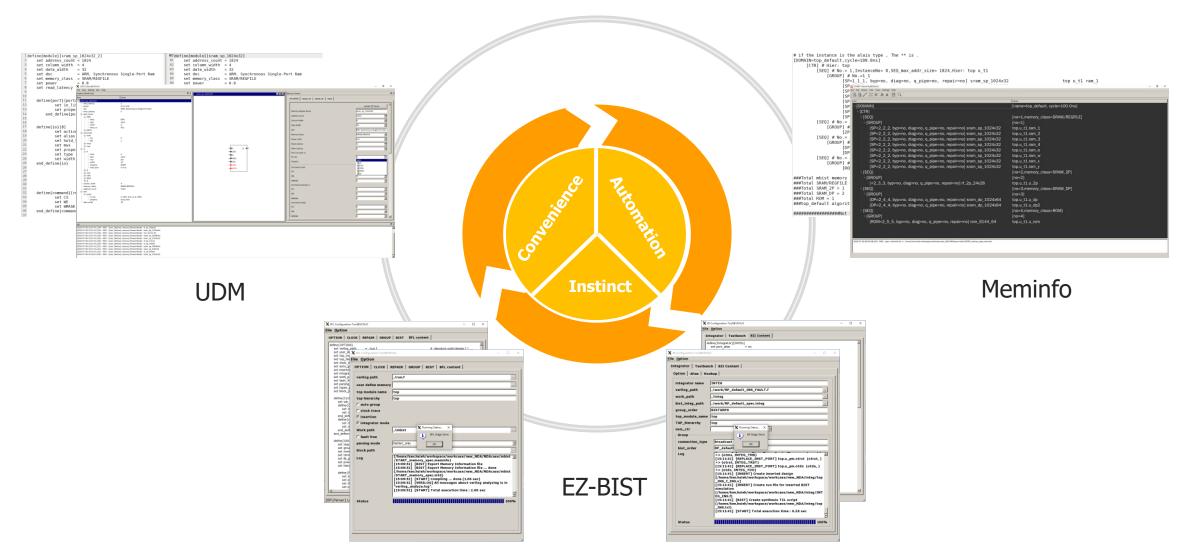

#### **Friendly Graphical User Interface**

#### **Performance Enhancement Instances**

- E-Company

- In house solution

- Around 100 memory instances

- Foreign A-Company

- Using other brand tool

- Above 2000 memory instances

# 客製化不是奢華要求,是芯測基本的設計方針 Customized Design Is Basic Not Luxurious Requirement

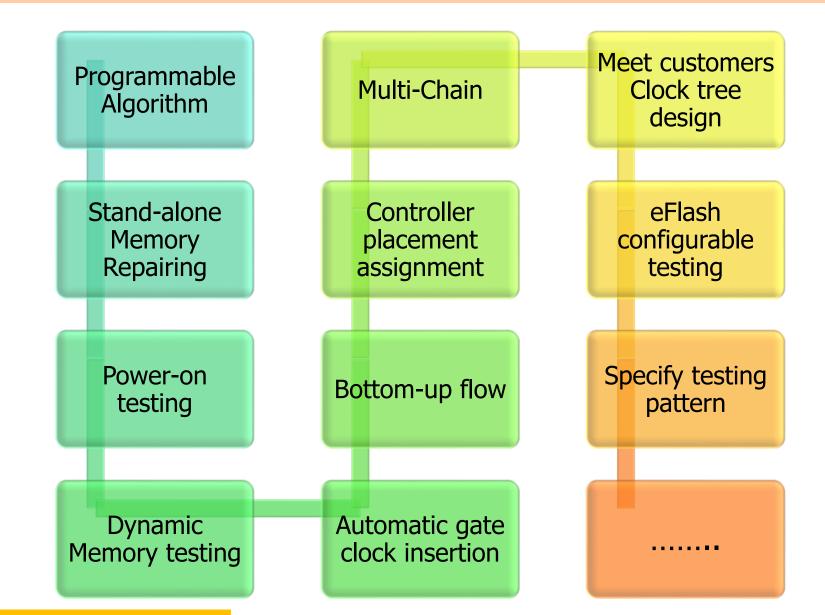

#### **Customized Requirements in MBIST & MBISR**

Meet design flow

Meet application scenario

Low power design

Low gate count design

High defect coverage

Memory defects analysis

Repairing for memory without redundancy

User define testing algorithm

#### **Customized Functionalities List**

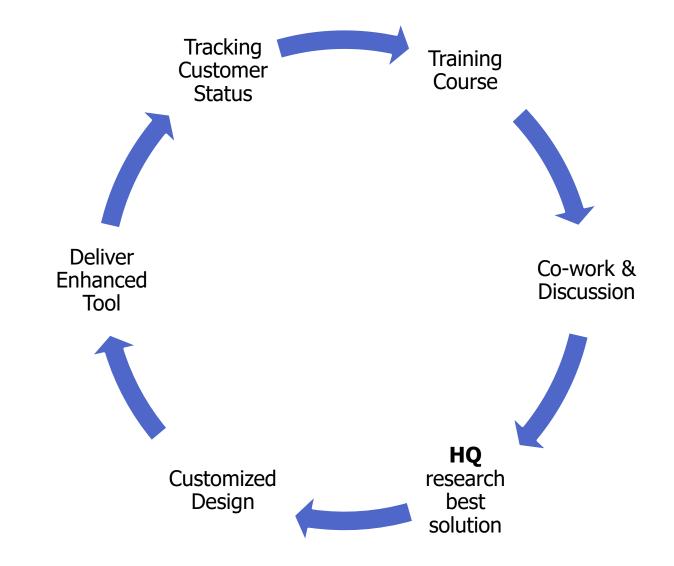

# 今天我想來點...技術支持-Delivery Service Delivery Service — Always Deliver What You Need Technical Service

## **Benefits of Delivery Service**

- **♦**No traveling time & money

- **♦** Reduce survey time

- **♦**Get goods in time

- **♦**Without transport effort

- **♦** More choice on APP

- **♦**Price comparison

## **iSTART** Delivery Service Flow

#### **Topic Events**

- **♦iSTART-Day**

- **◆**Technical forum

- **♦**Webinar

- **♦**White paper

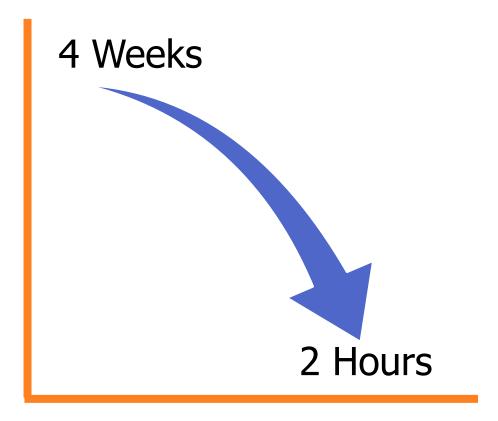

#### **ELAN** uses **EZ-BIST** to speed up **DFT** design

《半導體》芯測打入義隆 縮短記憶體測試電路開發時程 95%

● 時報資訊

時報資訊

2020年10月15日 上午10:33

【時報-台北電】亞洲唯一記憶體測試與修復技術領導廠商芯測科技(6786)宣布義隆電子(2458)導入芯測 EZ-BIST便捷版記憶體測試電路開發工具(EDA),作為開發晶片時記憶體測試電路設計的關鍵工具;經實測,透過此工具可大幅縮短記憶體測試電路開發時程約95%。

芯測表示,公司處於IC設計產業鏈的上游,提供EDA工具與IP給IC設計公司、設計服務公司、半導體製造商等,藉由「EDA工具」與「IP」縮短IC設計開發時程,提升SoC良率。而公司主要營收來源則是來自於EDA工具的簽約金以及IP授權金。

所謂EDA是指利用電腦軟體工具將複雜的電子產品設計過程自動化,協助工程師在設計電子產品時,可以縮短產品開發時間,提高市場競爭力。而SoC則是將數個功能不同的晶片,整合成一個具有完整功能的晶片,再封裝成一個積體電路,稱為「系統單晶片(System on a Chip)」;SoC的重要性在於其能減少體積、降低成本以及提升效能。然而,要將數個功能不同的晶片整合在一個SoC中,不論在製造、封裝、測試上均有一定的難度,因此隨著手機、高性能運算、IoT、車用電子、消費性電子需求及效能日益增加,記憶體測試與修復技術亦日趨重要。

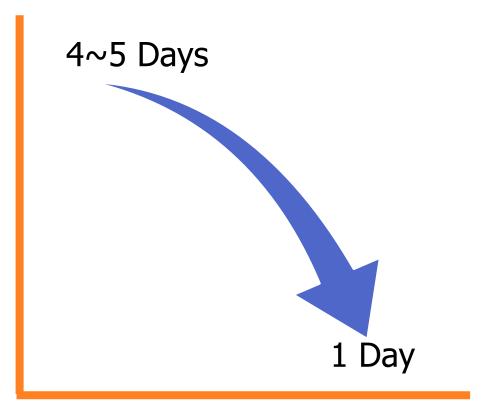

## ITE uses specific repairing solution of START

2019-09-26

聯陽半導體採用芯測科技START記憶體測試與修復整合性電路開發環境

#### 有效提升晶片良率與降低芯片成本

【台灣新竹】深耕於開發記憶體測試與修復技術的**芯測科技(iSTART-Tek·簡稱iSTART)**·宣布SRAM的測試與修復整合性電路開發環境-**START**獲得**聯陽半導體(ITE·簡稱聯陽)**採用。芯測科技的START解決方案透過可支援Stand-Alone SRAM的**Soft-Repair**技術來修復損壞記憶體,不需要使用額外備援記憶體,且不增加芯片成本·其電路面積也較小,可幫助客戶提升良率並降低開發成本。

芯測科技(iSTART)所研發的記憶體測試與修復整合性電路開發環境-START是Tool-Based的解決方案,可自動生成內嵌(Built-in)記憶體測試和修復電路並導入客戶設計中,其產生的電路面積小並可以提供客製化功能設計協助。而START中Soft-Repair修復方式利用沒有使用到的SRAM(Stand-Alone SRAM)作為記憶體修復時需要的備援記憶體。特性為不需要額外的非揮發性記憶體與控制電路來儲存修復相關設定資訊,因此可以節省整體晶片的面積,且晶片效能也不會被非揮發性記憶體的存取速度所侷限。此外,芯測科技的產品工具友善度極高,再加上圖形化使用者介面(GUI),大大提升使用方便性,在配合技術人員的即時支援,可快速解決客戶不同需求,協助客戶提高設計效率並滿足客戶不同應用的需求,更大幅提升晶片良率與降低芯片開發成本;再加上也實現矽晶驗證(Silicon-Proven)的紀錄,代表芯測的產品已完全達到業界要求,亦不會被製程是否支援備援記憶體模組而限制,大大提升設計的彈性。

#### 關於聯陽半導體:

聯陽半導體股份有限公司 (ITE Tech. Inc.,以下簡稱聯陽) 成立於1996年,總公司設在新竹科學工業園區,是一家專業的 Fabless IC 設計公司, 早期深耕PC及NB控制晶片的 開發設計,其Super I/O (輸出入晶片)及Keyboard and Embedded Controller晶片技術已是全球領導者, 客戶群涵蓋各主要個人電腦製造廠商。隨著公司穩健發展,聯陽逐漸擴展產品及技術領域,核心技術涵蓋High Speed Serial Interface、 Video Codec、Touch Sensing、 Surveillance、 OFDM、 Sensor Fusion 等。

#### **M31 uses START in Memory Compiler IP**

2019-10-16

芯測科技宣布円星科技(M31)採用START於 SRAM Compiler IP解決方案中

【台灣新竹】新興市場市場包含人工智慧(AI)、IoT與車用電子晶片對於SRAM的需求與日俱增,這些新興市場市場正為人類與科技間的互動方式帶來革命性的影響,上述應用的晶片設計商無不在尋求高可靠度、高性能的SRAM IP。而深耕於開發記憶體測試與修復技術的**芯測科技(iSTART-Tek**·簡稱iSTART)的START(記憶體測試與修復整合性電路開發環境)獲得円星科技(M31 Technology Corporation)使用於SRAM Compiler IP解決方案中。円星科技(M31)透過芯測科技START所產生的記憶體測試電路,充分驗證円星科技(M31) SRAM Compiler IP的可靠度,以滿足客戶在高速SRAM Compiler IP的需求。

「円星科技很高興成為芯測科技的合作夥伴。」円星科技(M31)副總經理連南鈞表示「在研發的過程中,芯測科技針對SRAM Compiler IP驗證提供完整且高效的測試方式, 能快速簡便的產生記憶體內建測試電路,滿足M31(円星)在記憶體測試的要求,可提供客戶最具競爭力的IP,同時也充分驗證芯測科技所提供的記憶體內建測試電路方案。」

「芯測科技很高興能與M31(円星)建立長期互相合作的關係,透過芯測科技的START和專業的服務,使得M31可以在最短的時間內完成高速記憶體IP的驗證。」芯測科技副總經理張容誠表示「未來將與M31在次世代先進記憶體上有更進一步的合作,以面對新興市場的挑戰。」

芯測科技(iSTART)所研發的記憶體測試與修復整合性電路開發環境-START,擁有完整的測試算法、易於使用的圖像化工具操作介面,與技術的即時支援,滿足客戶高速SRAM 測試需求,協助客戶提高設計效率。

#### 關於円星科技 (M31 Technology)

円星科技成立於2011年10月,是專業的矽智財 (Silicon Intellectual Property) 開發商。円星科技擁有非常堅強的研發與服務團隊,具備矽智財、積體電路設計以及設計自動 化領域的資深工作經驗。主要產品包括高速介面矽智財設計如USB、PCIe、MIPI、SATA等,以及基礎矽智財如元件庫(Cell Library)設計,記憶體設計(Memory Design),和靜電防護輸出入庫(ESD/IO library)。円星科技的願景是成為半導體產業最值得信賴的矽智財公司。更詳細資料請參考公司網頁 https://www.m31tech.com

#### **ASICLAND** adopt **START** tool to AI chip

2019-11-28

芯測科技獲韓國Asic Land青睞 採用於AI應用晶片上

【台灣新竹】隨著AI應用越趨多元、運算能力的需求不斷提升。AI晶片內含複雜的類神經網路,需要大量的運算資源才能執行。所以,AI晶片對於記憶體的需求大幅增加,對於記憶體的可靠度需求也相對提升。此外,因為AI晶片的單價高,因此,AI晶片對於記憶體修復有著高度的依賴。深耕於開發記憶體測試與修復技術的芯測科技(iSTART-Tek,簡稱iSTART)宣布SRAM的測試與修復整合性電路開發環境-START獲得韓國Asic Land使用於AI應用晶片中。ASICLand的設計復雜且記憶體數量廳大,因此使用了芯測科技START的新功能「Bottom-Up Flow」加速複雜SoC內部的記憶體整合並快速產生記憶體測試與修復電路。START提供客戶系統性的流程,不需太過繁複的設定過程即可完成記憶體測試與修復電路。START的彈性化的設計方式,提供Multi-eFuse架構,使客戶能夠透過多顆eFuse來進行記憶體修復。另外,START提供多元化的記憶體種類支持,透過芯測科技專業的技術服務協助客戶在台積電 (TSMC) 28nm製程下完成測試與修復電路的產生。

「韓國Asic Land是台積電 (TSMC) 價值鏈聚合聯盟 (VCA) 和ARM認可的設計合作夥伴 (ADP),是一家領先業界之ASIC / SoC設計服務提供商,擁有高度集成的技術和專有技術的公司,也專注於AI、5G、區塊鏈和物聯網等。」客戶銷售部協理李玉如表示:「近期因應時代需求與新興市場的挑戰,Asic Land投入了具前瞻性的AI項目計畫,芯測科技很榮幸參與其中。透過芯測科技的START工具和即時專業的服務,即便是龐大複雜的SoC,也可藉由工具的自動化功能與雙方研發園隊有效率的溝通合作,在最短的時間內完成此項目。」

基於複雜演算法架構下的AI晶片對於記憶體的需求與日俱增,所以記憶體的可靠度與整體晶片成本更加被重視。以至於對於記憶體的測試與修復技術的要求也相對提高許多。芯測科技的START幫助使用者提高生產率並有效降低產品開發的時程,提升產品可靠度並有效的延長產品的使用壽命。

關於Asic Land Co., Ltd:

芯測將和你一起走向數位新世代

Prospect of iSTART and You

#### **iSTART Faith & Core Value**

#### **◆Innovation**

- Develop advanced MBIST/MBISR technology

- Research new algorithm to improve coverage

- Develop new algorithm for new memory model

#### **♦**Service

- Shorten customers learning curve

- Provide best technical consult

- Comply customer's needs before customer's request

#### **◆**Efficient

- Implement efficient mindset into each aspect

- Work closely with customers

- Let customers acquire best solution rapidly

#### **Total Solutions Chain of iSTART**

**Memory Scan Insertion Testing & Repairing ISTART** AP&R **Turnkey Solution**

# Prospect of START v2 & SoC

In response to the 5G generation, AI, AIoT, Automotive chips would enter another generation.

To increase computing capability, Multi-core structure would be a standard ones in advanced chip.

iSTART has foresee the marketing trend, planning to launch Multicore structure solution to meet customers' needs of MBIST.

# Google

Q 芯測科技