深耕於開發記憶體測試與修復技術的芯測科技(iSTART-TEK,股票代號6786),宣佈旗下EZ-BIST記憶體測試電路開發平台獲華潤微電子有限公司(華潤微)採用,作為開發晶片時,記憶體測試電路設計的關鍵工具,透過此工具可有效縮短記憶體測試電路的開發時程。

芯測科技位於IC設計產業鏈的上游,提供EDA工具與IP給IC設計公司、設計服務公司、半導體製造商等,藉由「EDA工具」與「IP」縮短IC設計開發時程,提升SoC良率。

芯測科技提到,第二季開始,部分半導體廠代工廠出現產能供過於求的雜音,如此一來,IC設計公司便開始思考開發新的晶片,芯測科技受惠於這樣的情況,近期業績也開始回溫。

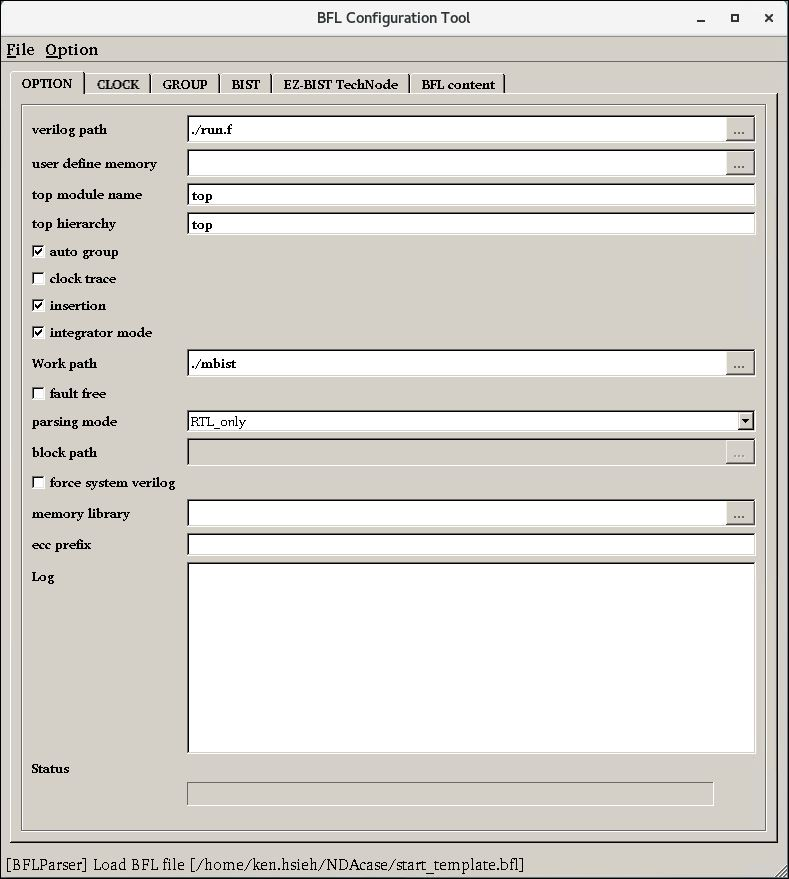

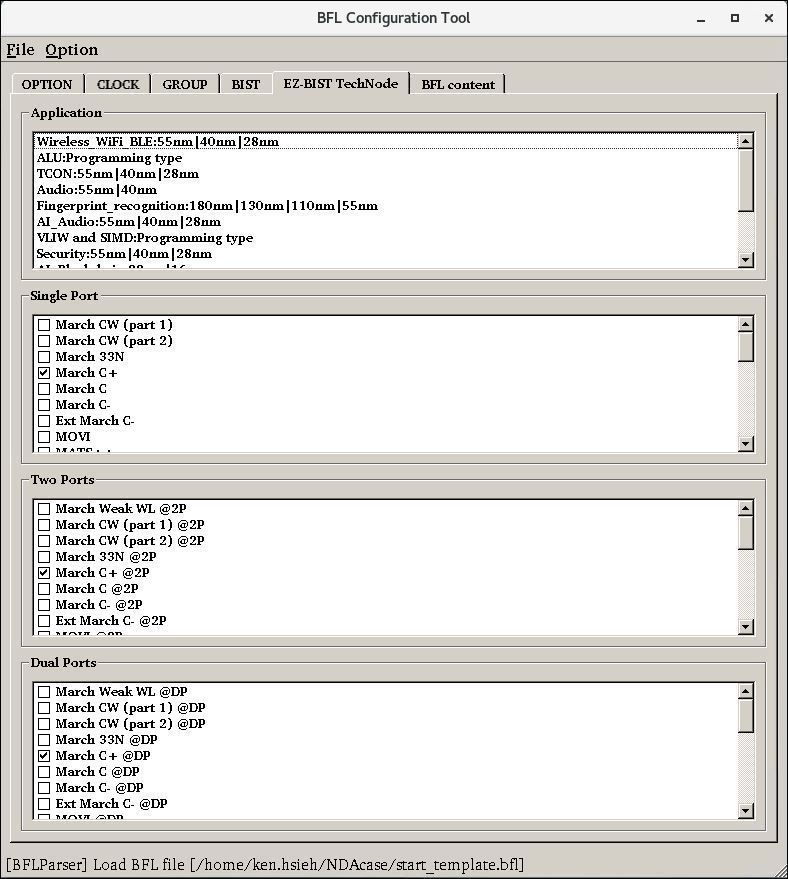

為了秉持著幫助開發者以更簡單、更快速、更低成本的途徑實現SOC設計的初衷,芯測科技推出完全以圖形化操作介面「GUI」為主的EZ-BIST(如下方,圖一),並可完全依靠圖形化操作介面產生BIST電路的EDA工具,並在圖形化操作介面中,內建了許多記憶體測試演算法(如下方,圖二),讓使用者可以根據晶片開發的製程與應用,來選擇最適當的演算法,同時提供了「防呆」功能來避免人為操作工具時的錯誤發生,進而讓記憶體演算法的電路實現變得更加容易。

圖一

圖二

芯測表示,EZ-BIST的優勢在於有效的降低DPPM(Defect Part Per Million,每百萬件不良率)、簡單的操作流程容易被晶片設計工程師接受以及內建豐富的記憶體測試演算法。

展望未來,芯測指出,如何精準找出記憶體缺陷以及如何降低DPPM(Defect Part Per Million,每百萬件不良率),是各家IC設計公司與晶片開發商專注的重點之一,而採用專業的記憶體測試EDA工具,將可望有效降低DPPM、提高晶片品質。